KS152JB Universal Communications Controller Technical Specifications

UR - Underrun Flag, see TSTAT.

XRCLK - External GSC Receive Clock Enable bit, see PCON.

XTCLK - External GSC Transmit Clock Enable bit, see GMOD.

...............................

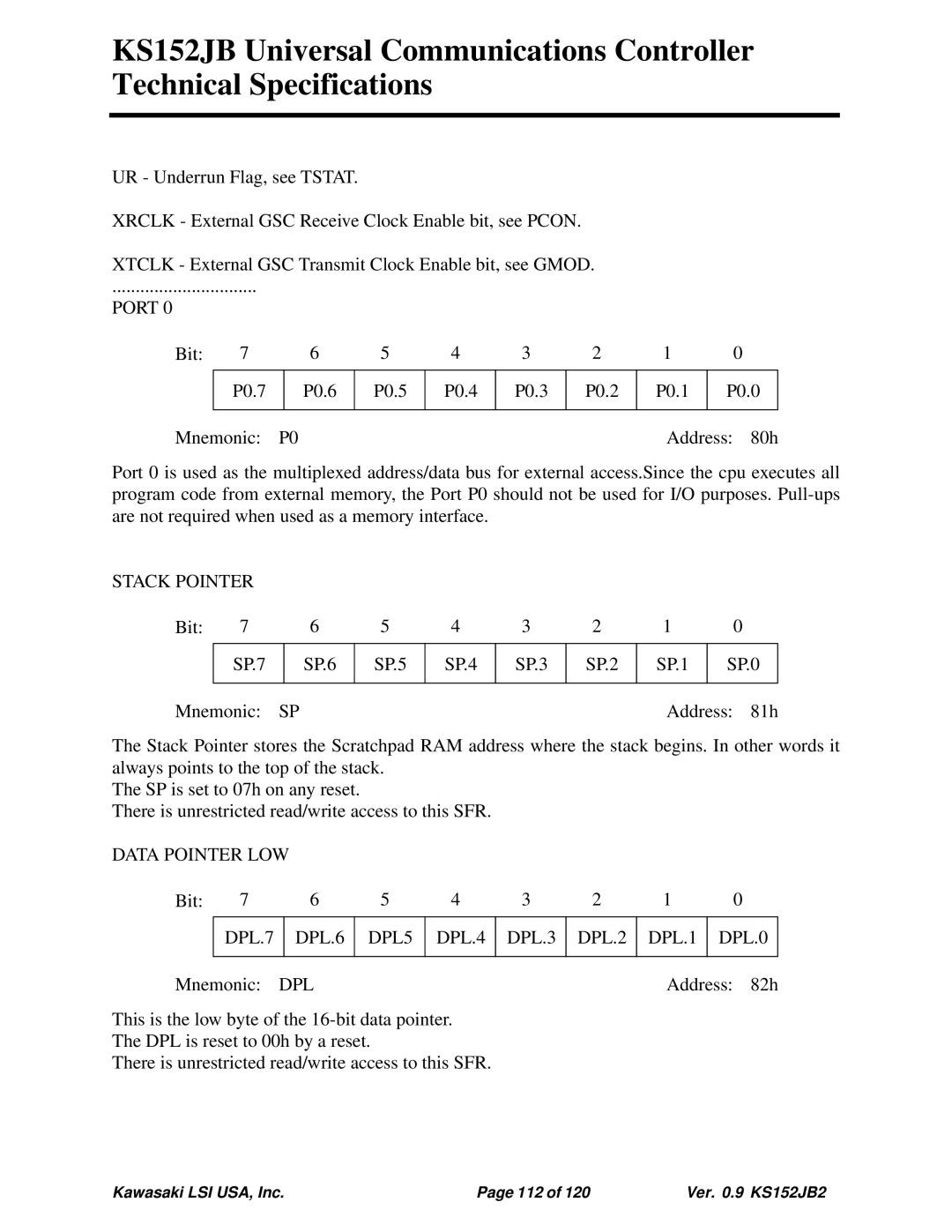

PORT 0

Bit: | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

|

|

|

|

|

|

|

|

|

|

| P0.7 |

| P0.6 | P0.5 | P0.4 | P0.3 | P0.2 | P0.1 | P0.0 |

|

|

|

|

|

|

|

|

|

|

Mnemonic: | P0 |

|

|

|

| Address: 80h | |||

Port 0 is used as the multiplexed address/data bus for external access.Since the cpu executes all program code from external memory, the Port P0 should not be used for I/O purposes.

STACK POINTER |

|

|

|

|

|

|

|

| |

Bit: | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

|

|

|

|

|

|

|

|

|

|

| SP.7 |

| SP.6 | SP.5 | SP.4 | SP.3 | SP.2 | SP.1 | SP.0 |

|

|

|

|

|

|

|

|

|

|

Mnemonic: | SP |

|

|

|

| Address: 81h | |||

The Stack Pointer stores the Scratchpad RAM address where the stack begins. In other words it always points to the top of the stack.

The SP is set to 07h on any reset.

There is unrestricted read/write access to this SFR.

DATA POINTER LOW

Bit: | 7 | 6 | 5 | 4 | 3 | 2 | 1 |

| 0 | |

|

|

|

|

|

|

|

|

| ||

| DPL.7 | DPL.6 | DPL5 | DPL.4 | DPL.3 | DPL.2 | DPL.1 | DPL.0 | ||

|

|

|

|

|

|

|

|

|

|

|

Mnemonic: | DPL |

|

|

|

| Address: | 82h | |||

This is the low byte of the

The DPL is reset to 00h by a reset.

There is unrestricted read/write access to this SFR.

Kawasaki LSI USA, Inc. | Page 112 of 120 | Ver. 0.9 KS152JB2 |