KS152JB Universal Communications Controller Technical Specifications

If a transmitting 8XC152 detects a collision during the preamble/BOF part of the frame that it is trying to transmit, it will complete the preamble/BOF and then begin the jam signal in the first bit time after BOF. If the collision is detected later in the frame., the jam signal will begin in the next bit time after the collision was detected.

The jam signal lasts for the same number of bit times as the selected CRC

The 8XC152 provides two types of jam signals that can be selected by user software. If the node is

When the jam signal is completed, the 8XC152 goes into an idle state. Presumably, other stations on the network are also generating their own jam signals, after which they too go into an idle state. When the 8XC152 detects the idle state at its own GRXD pin, the backoff sequence begins.

Backoff

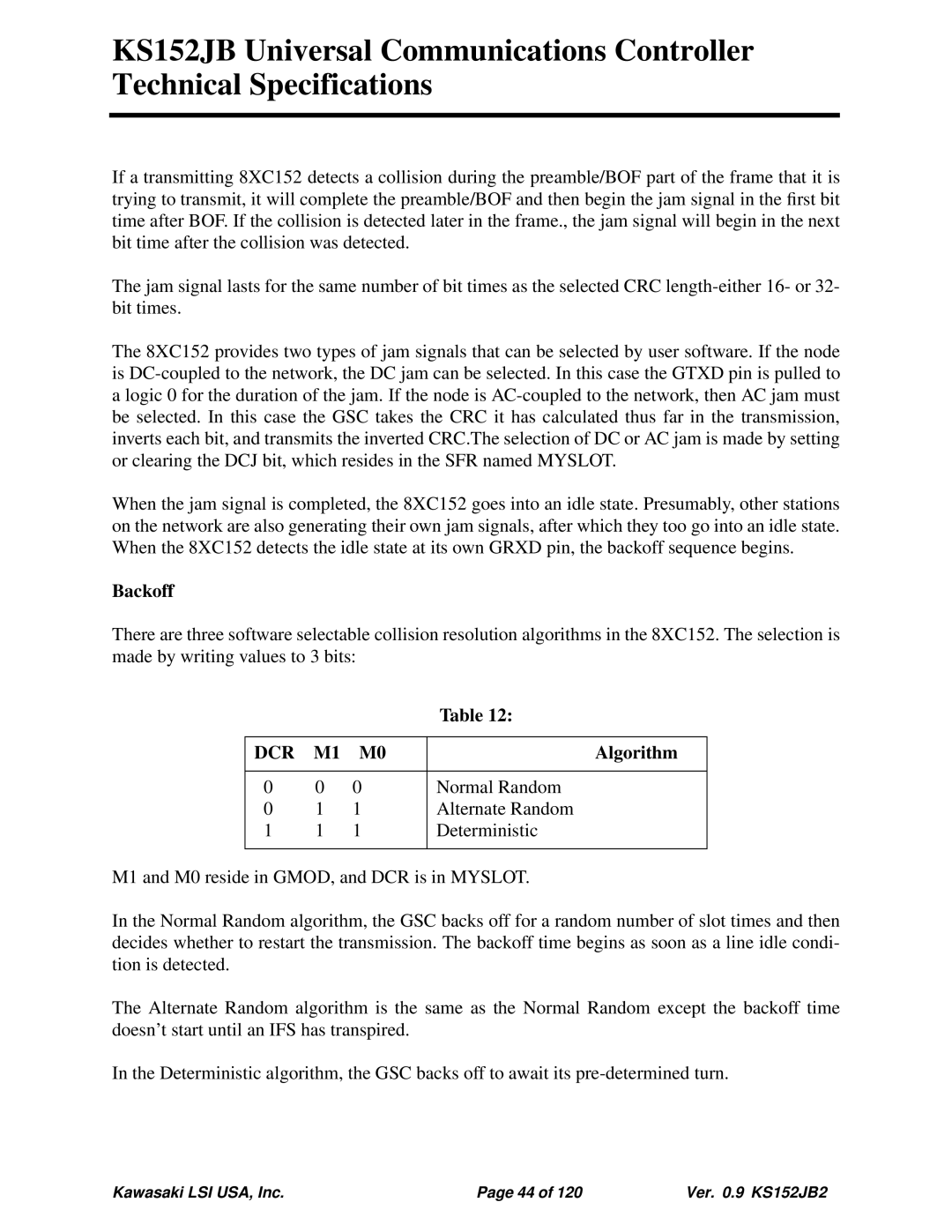

There are three software selectable collision resolution algorithms in the 8XC152. The selection is made by writing values to 3 bits:

|

|

| Table 12: |

|

|

|

|

DCR | M1 | M0 | Algorithm |

|

|

|

|

0 | 0 | 0 | Normal Random |

0 | 1 | 1 | Alternate Random |

1 | 1 | 1 | Deterministic |

|

|

|

|

M1 and M0 reside in GMOD, and DCR is in MYSLOT.

In the Normal Random algorithm, the GSC backs off for a random number of slot times and then decides whether to restart the transmission. The backoff time begins as soon as a line idle condi- tion is detected.

The Alternate Random algorithm is the same as the Normal Random except the backoff time doesn’t start until an IFS has transpired.

In the Deterministic algorithm, the GSC backs off to await its

Kawasaki LSI USA, Inc. | Page 44 of 120 | Ver. 0.9 KS152JB2 |