KS152JB Universal Communications Controller Technical Specifications

As shown in Figure above, the Receive Valid interrupt can be signalled either by the RFNE flag (Receive FIFO Not Empty), or by the RDN flag (Receive Done). Which one of these flags causes the interrupt depends on the setting of the DMA bit in the SFR named TSTAT.

DMA = 0 means the DMA hardware is not configured to service the GSC, so the CPU will service it in software in response to the Receive FIFO not being empty. In that case, RFNE generates the Receive Valid interrupt.

DMA = 1 means the DMA hardware is configured to service the GSC, in which case the CPU need not be interrupted till the receive is complete. In that case RDN generates the Receive Valid interrupt.

Similarly the Transmit Valid interrupt can be signalled either by the TFNF flag (Transmit FIFO Not Full), or by the TDN flag (Transmit Done), depending on whether the DMA bit is 0 or 1.

Note that setting the DMA bit does not itself configure the DMA channels to service the GSC. That job must be done by software writes to the DMA registers. the DMA bit only selects whether the GSCRV and GSCTV interrupts are flagged by a FIFO needing service or by an “operation done” signal.

The Receive and Transmit Error interrupt flags are generated by the logical OR of a number of error conditions, which are described in Section 3.6.5.

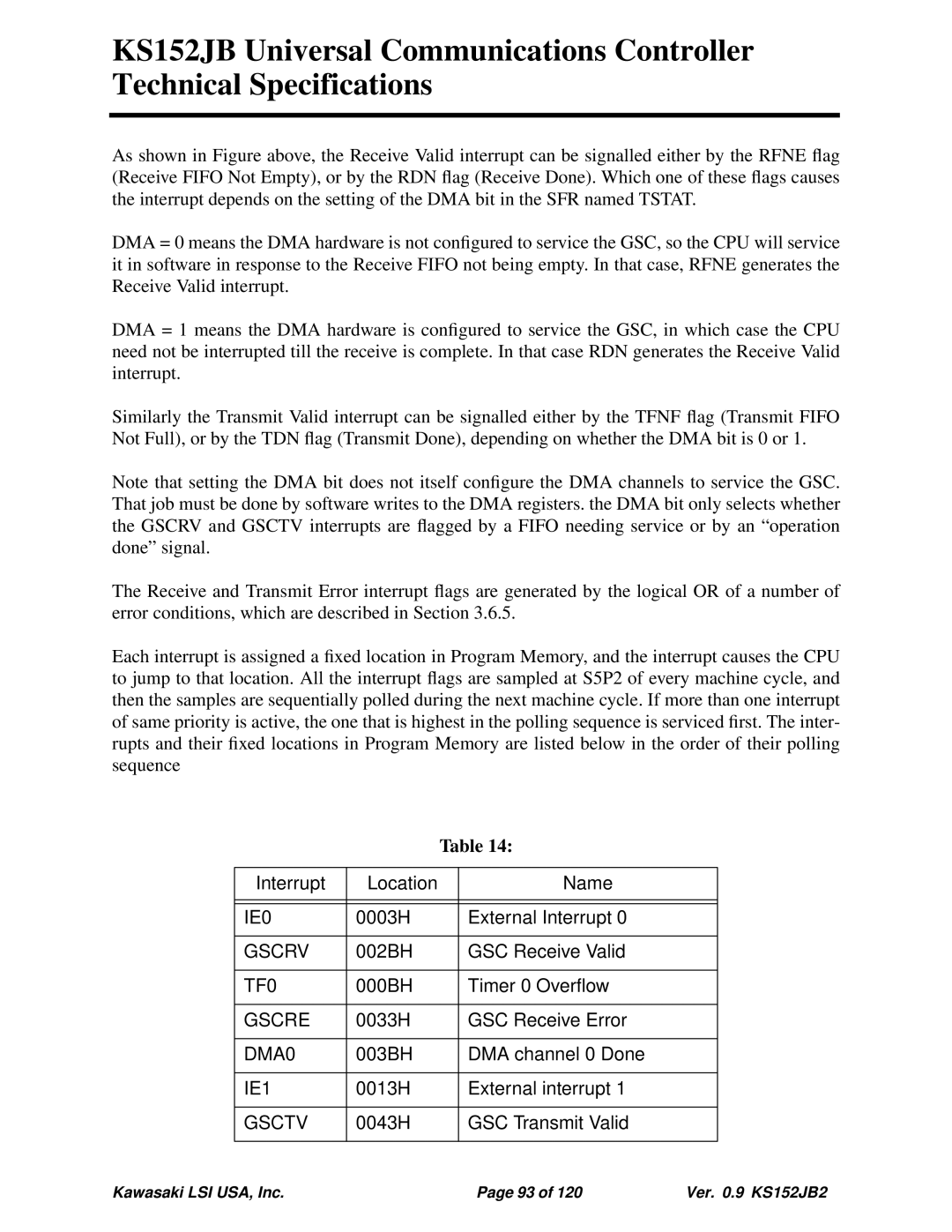

Each interrupt is assigned a fixed location in Program Memory, and the interrupt causes the CPU to jump to that location. All the interrupt flags are sampled at S5P2 of every machine cycle, and then the samples are sequentially polled during the next machine cycle. If more than one interrupt of same priority is active, the one that is highest in the polling sequence is serviced first. The inter- rupts and their fixed locations in Program Memory are listed below in the order of their polling sequence

|

| Table 14: | |

|

|

|

|

Interrupt | Location |

| Name |

|

|

|

|

|

|

|

|

IE0 | 0003H |

| External Interrupt 0 |

|

|

|

|

GSCRV | 002BH |

| GSC Receive Valid |

|

|

|

|

TF0 | 000BH |

| Timer 0 Overflow |

|

|

|

|

GSCRE | 0033H |

| GSC Receive Error |

|

|

|

|

DMA0 | 003BH |

| DMA channel 0 Done |

|

|

|

|

IE1 | 0013H |

| External interrupt 1 |

|

|

|

|

GSCTV | 0043H |

| GSC Transmit Valid |

|

|

|

|

Kawasaki LSI USA, Inc. | Page 93 of 120 | Ver. 0.9 KS152JB2 |