KS152JB Universal Communications Controller Technical Specifications

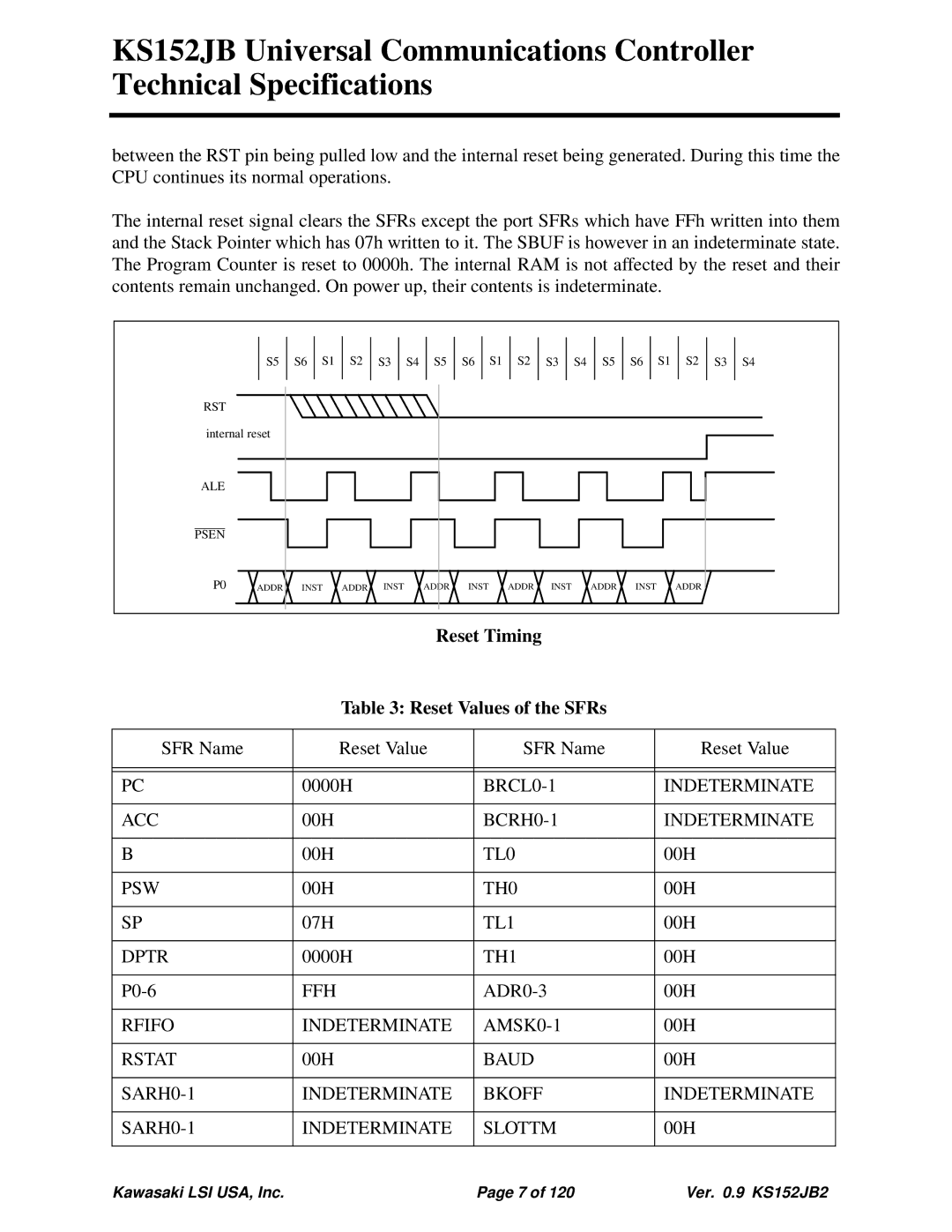

between the RST pin being pulled low and the internal reset being generated. During this time the CPU continues its normal operations.

The internal reset signal clears the SFRs except the port SFRs which have FFh written into them and the Stack Pointer which has 07h written to it. The SBUF is however in an indeterminate state. The Program Counter is reset to 0000h. The internal RAM is not affected by the reset and their contents remain unchanged. On power up, their contents is indeterminate.

| S5 | S6 | S1 | S2 | S3 | S4 | S5 | S6 | S1 | S2 | S3 | S4 | S5 | S6 | S1 | S2 | S3 | S4 |

RST |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

internal reset |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

ALE |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

PSEN |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

P0 | ADDR | INST | ADDR | INST |

| ADDR | INST |

| ADDR | INST |

| ADDR | INST |

| ADDR |

|

| |

Reset Timing

Table 3: Reset Values of the SFRs

SFR Name | Reset Value | SFR Name | Reset Value |

|

|

|

|

|

|

|

|

PC | 0000H | INDETERMINATE | |

|

|

|

|

ACC | 00H | INDETERMINATE | |

|

|

|

|

B | 00H | TL0 | 00H |

|

|

|

|

PSW | 00H | TH0 | 00H |

|

|

|

|

SP | 07H | TL1 | 00H |

|

|

|

|

DPTR | 0000H | TH1 | 00H |

|

|

|

|

FFH | 00H | ||

|

|

|

|

RFIFO | INDETERMINATE | 00H | |

|

|

|

|

RSTAT | 00H | BAUD | 00H |

|

|

|

|

INDETERMINATE | BKOFF | INDETERMINATE | |

|

|

|

|

INDETERMINATE | SLOTTM | 00H | |

|

|

|

|

Kawasaki LSI USA, Inc. | Page 7 of 120 | Ver. 0.9 KS152JB2 |