KS152JB Universal Communications Controller Technical Specifications

The TL1 sfr is set to 00h on any reset.

There is unrestricted read/write access to this SFR.

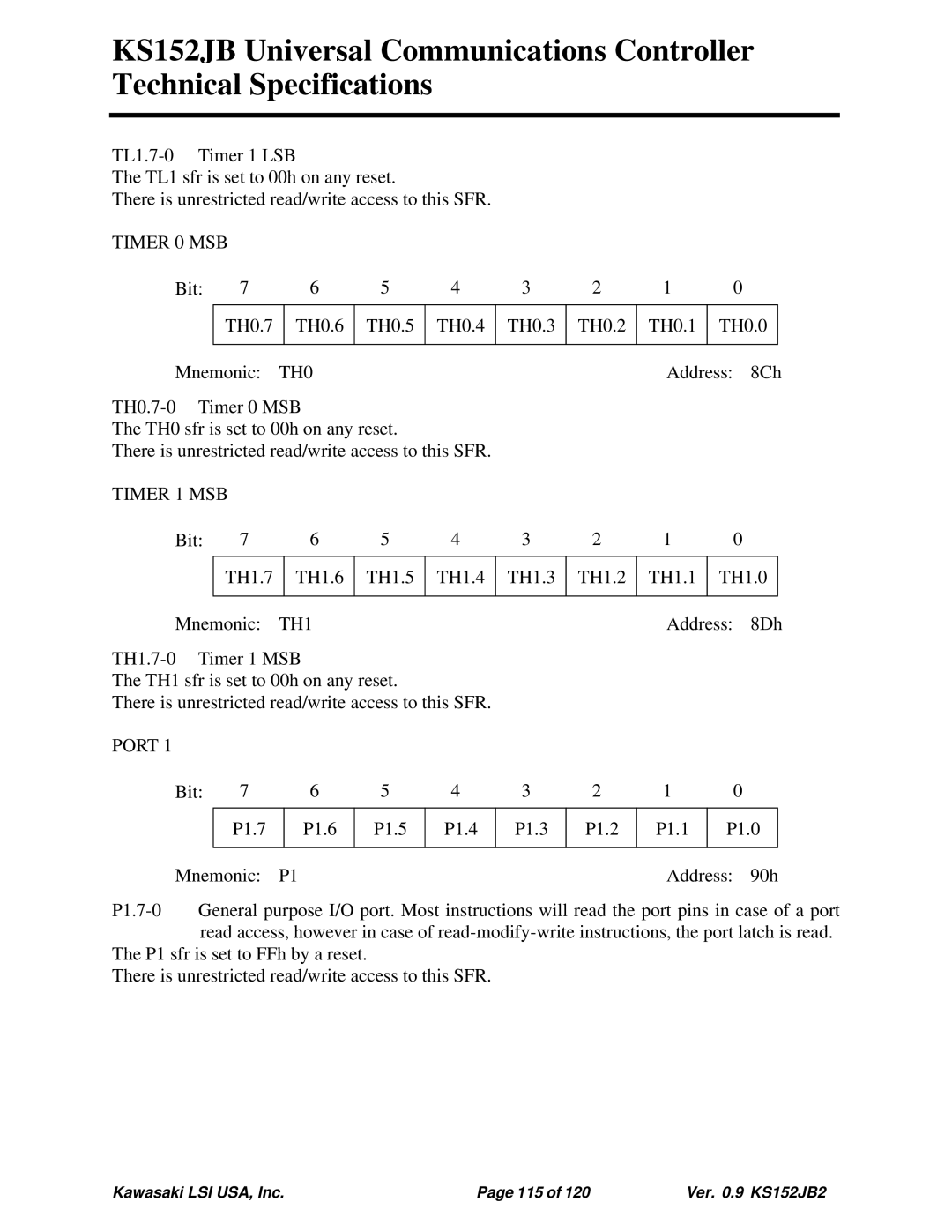

TIMER 0 MSB

Bit: | 7 | 6 | 5 | 4 | 3 | 2 | 1 |

| 0 |

| ||

|

|

|

|

|

|

|

|

|

|

|

| |

|

| TH0.7 |

| TH0.6 | TH0.5 | TH0.4 | TH0.3 | TH0.2 | TH0.1 | TH0.0 |

| |

|

|

|

|

|

|

|

|

|

|

|

| |

Mnemonic: | TH0 |

|

|

|

| Address: | 8Ch | |||||

Timer 0 MSB |

|

|

|

|

|

|

|

| ||||

The TH0 sfr is set to 00h on any reset. |

|

|

|

|

|

|

| |||||

There is unrestricted read/write access to this SFR. |

|

|

|

|

|

| ||||||

TIMER 1 MSB |

|

|

|

|

|

|

|

|

|

| ||

Bit: | 7 | 6 | 5 | 4 | 3 | 2 | 1 |

| 0 |

| ||

|

|

|

|

|

|

|

|

|

|

| ||

|

| TH1.7 |

| TH1.6 | TH1.5 | TH1.4 | TH1.3 | TH1.2 | TH1.1 | TH1.0 |

| |

|

|

|

|

|

|

|

|

|

|

|

| |

Mnemonic: | TH1 |

|

|

|

| Address: | 8Dh | |||||

Timer 1 MSB |

|

|

|

|

|

|

|

| ||||

The TH1 sfr is set to 00h on any reset. |

|

|

|

|

|

|

| |||||

There is unrestricted read/write access to this SFR. |

|

|

|

|

|

| ||||||

PORT 1 |

|

|

|

|

|

|

|

|

|

|

|

|

Bit: | 7 | 6 | 5 | 4 | 3 | 2 | 1 |

| 0 |

| ||

|

|

|

|

|

|

|

|

|

|

| ||

|

| P1.7 |

| P1.6 | P1.5 | P1.4 | P1.3 | P1.2 | P1.1 | P1.0 |

| |

|

|

|

|

|

|

|

|

|

|

|

| |

Mnemonic: | P1 |

|

|

|

| Address: | 90h | |||||

The P1 sfr is set to FFh by a reset.

There is unrestricted read/write access to this SFR.

Kawasaki LSI USA, Inc. | Page 115 of 120 | Ver. 0.9 KS152JB2 |