Programmer’s Model

The following sections describe the smc_pcell_id Registers:

•SMC PrimeCell Identification Register 0

•SMC PrimeCell Identification Register 1

•SMC PrimeCell Identification Register 2 on page

•SMC PrimeCell Identification Register 3 on page

Note

These registers cannot be read in the Reset state.

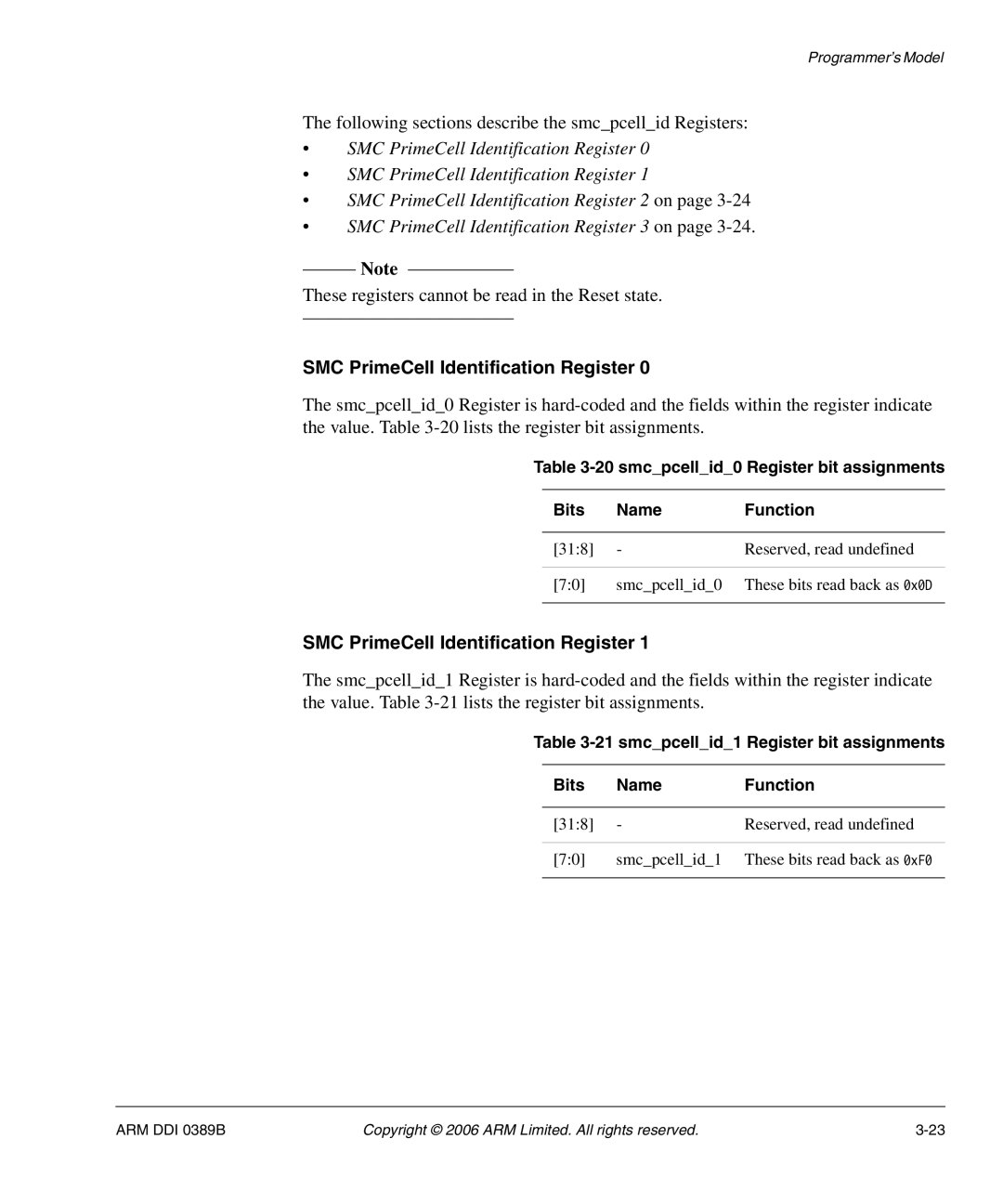

SMC PrimeCell Identification Register 0

The smc_pcell_id_0 Register is

Table 3-20 smc_pcell_id_0 Register bit assignments

Bits | Name | Function |

|

|

|

[31:8] | - | Reserved, read undefined |

|

|

|

[7:0] | smc_pcell_id_0 | These bits read back as 0x0D |

|

|

|

SMC PrimeCell Identification Register 1

The smc_pcell_id_1 Register is

Table 3-21 smc_pcell_id_1 Register bit assignments

Bits | Name | Function |

|

|

|

[31:8] | - | Reserved, read undefined |

|

|

|

[7:0] | smc_pcell_id_1 | These bits read back as 0xF0 |

|

|

|

ARM DDI 0389B | Copyright © 2006 ARM Limited. All rights reserved. |