Programmer’s Model

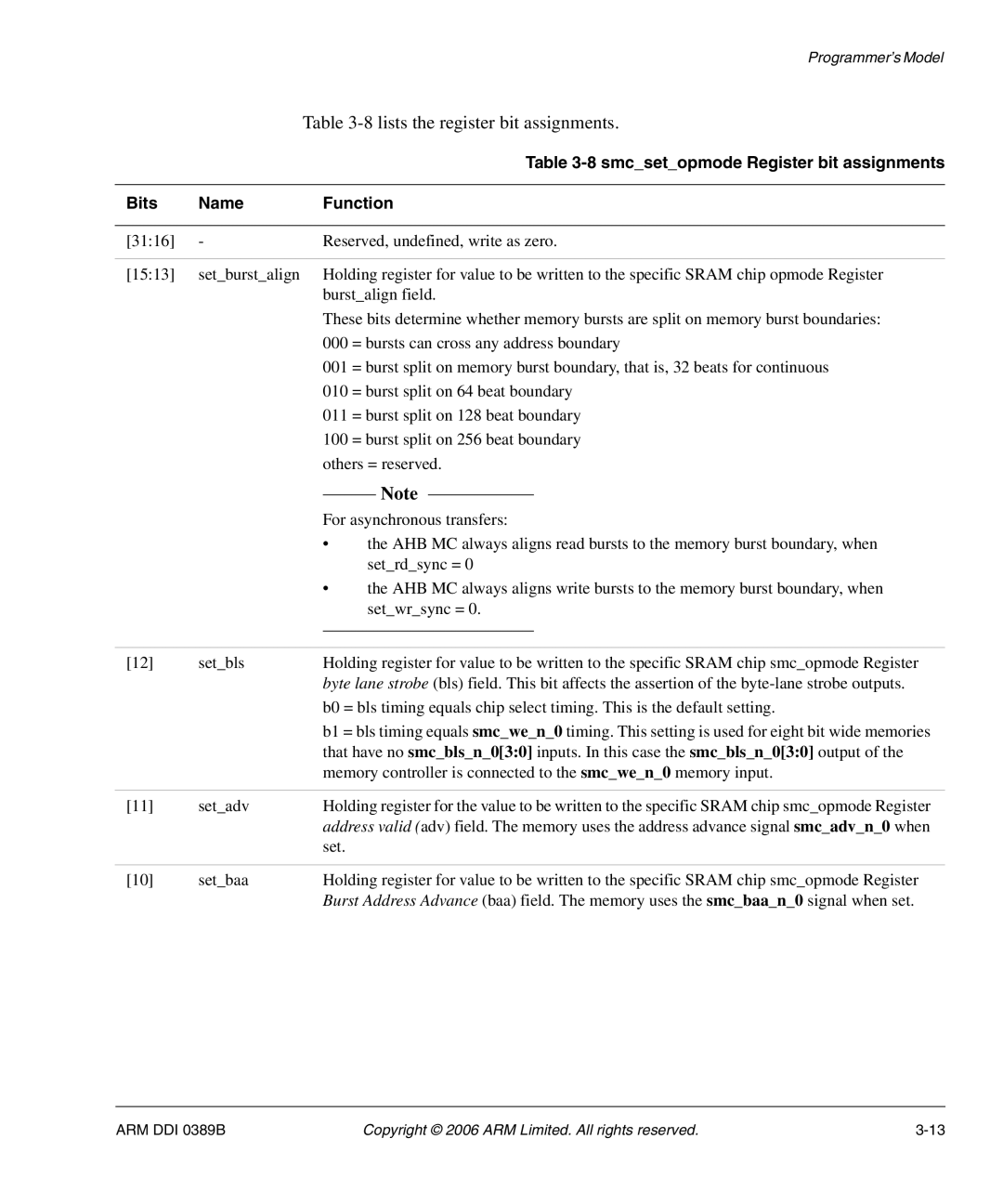

Table 3-8 lists the register bit assignments.

|

|

| Table |

|

|

| |

Bits | Name | Function | |

|

|

| |

[31:16] | - | Reserved, undefined, write as zero. | |

|

|

| |

[15:13] | set_burst_align | Holding register for value to be written to the specific SRAM chip opmode Register | |

|

| burst_align field. | |

|

| These bits determine whether memory bursts are split on memory burst boundaries: | |

|

| 000 | = bursts can cross any address boundary |

|

| 001 | = burst split on memory burst boundary, that is, 32 beats for continuous |

|

| 010 | = burst split on 64 beat boundary |

|

| 011 | = burst split on 128 beat boundary |

|

| 100 | = burst split on 256 beat boundary |

others = reserved.

Note

For asynchronous transfers:

• the AHB MC always aligns read bursts to the memory burst boundary, when set_rd_sync = 0

• the AHB MC always aligns write bursts to the memory burst boundary, when set_wr_sync = 0.

[12] | set_bls | Holding register for value to be written to the specific SRAM chip smc_opmode Register |

|

| byte lane strobe (bls) field. This bit affects the assertion of the |

|

| b0 = bls timing equals chip select timing. This is the default setting. |

|

| b1 = bls timing equals smc_we_n_0 timing. This setting is used for eight bit wide memories |

|

| that have no smc_bls_n_0[3:0] inputs. In this case the smc_bls_n_0[3:0] output of the |

|

| memory controller is connected to the smc_we_n_0 memory input. |

|

|

|

[11] | set_adv | Holding register for the value to be written to the specific SRAM chip smc_opmode Register |

|

| address valid (adv) field. The memory uses the address advance signal smc_adv_n_0 when |

|

| set. |

|

|

|

[10] | set_baa | Holding register for value to be written to the specific SRAM chip smc_opmode Register |

|

| Burst Address Advance (baa) field. The memory uses the smc_baa_n_0 signal when set. |

ARM DDI 0389B | Copyright © 2006 ARM Limited. All rights reserved. |