ADuC812

Using the D/A Converter

The

AVDD |

| ADuC812 |

|

| |

VREF | R |

|

| R | OUTPUT |

| BUFFER | |

|

| |

| R | 8 |

| R | |

| DISABLE | |

|

| (FROM MCU) |

| R |

|

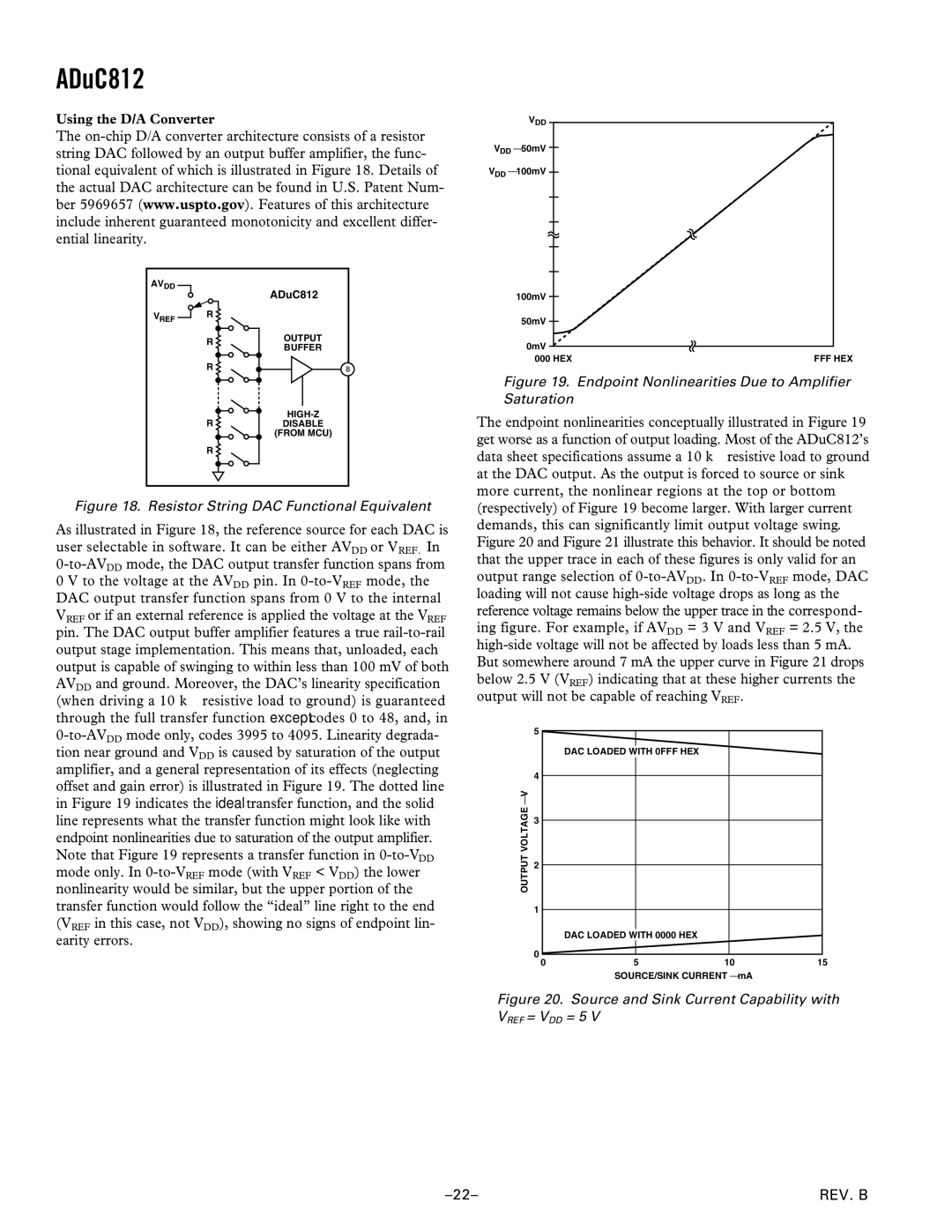

Figure 18. Resistor String DAC Functional Equivalent

As illustrated in Figure 18, the reference source for each DAC is

user selectable in software. It can be either AVDD or VREF. In

0V to the voltage at the AVDD pin. In

VREF or if an external reference is applied the voltage at the VREF pin. The DAC output buffer amplifier features a true

output stage implementation. This means that, unloaded, each output is capable of swinging to within less than 100 mV of both AVDD and ground. Moreover, the DAC’s linearity specification (when driving a 10 kΩ resistive load to ground) is guaranteed through the full transfer function except codes 0 to 48, and, in

mode only. In

transfer function would follow the “ideal” line right to the end

(VREF in this case, not VDD), showing no signs of endpoint lin- earity errors.

VDD |

|

VDD – 50mV |

|

VDD – 100mV |

|

100mV |

|

50mV |

|

0mV |

|

000 HEX | FFF HEX |

Figure 19. Endpoint Nonlinearities Due to Amplifier Saturation

The endpoint nonlinearities conceptually illustrated in Figure 19 get worse as a function of output loading. Most of the ADuC812’s data sheet specifications assume a 10 kΩ resistive load to ground at the DAC output. As the output is forced to source or sink more current, the nonlinear regions at the top or bottom (respectively) of Figure 19 become larger. With larger current demands, this can significantly limit output voltage swing. Figure 20 and Figure 21 illustrate this behavior. It should be noted that the upper trace in each of these figures is only valid for an

output range selection of

reference voltage remains below the upper trace in the correspond-

ing figure. For example, if AVDD = 3 V and VREF = 2.5 V, the

But somewhere around 7 mA the upper curve in Figure 21 drops below 2.5 V (VREF) indicating that at these higher currents the output will not be capable of reaching VREF.

| 5 |

|

|

|

|

|

|

|

|

|

| ITH 0FFF HEX |

|

|

|

| |

|

|

|

|

|

|

|

| |

|

|

| DAC LOADED W |

|

|

|

| |

– V | 4 |

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

|

|

|

|

|

|

|

| |

VOLTAGE | 3 |

|

|

|

|

|

|

|

OUTPUT | 2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

| 1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

| DAC LOADED W | ITH 0000 HEX |

|

|

|

|

| 0 |

|

|

|

|

|

|

|

| 0 | 5 | 10 | 15 | ||||

SOURCE/SINK CURRENT – mA

Figure 20. Source and Sink Current Capability with VREF = VDD = 5 V

REV. B |