ADuC812

SPECIAL FUNCTION REGISTERS

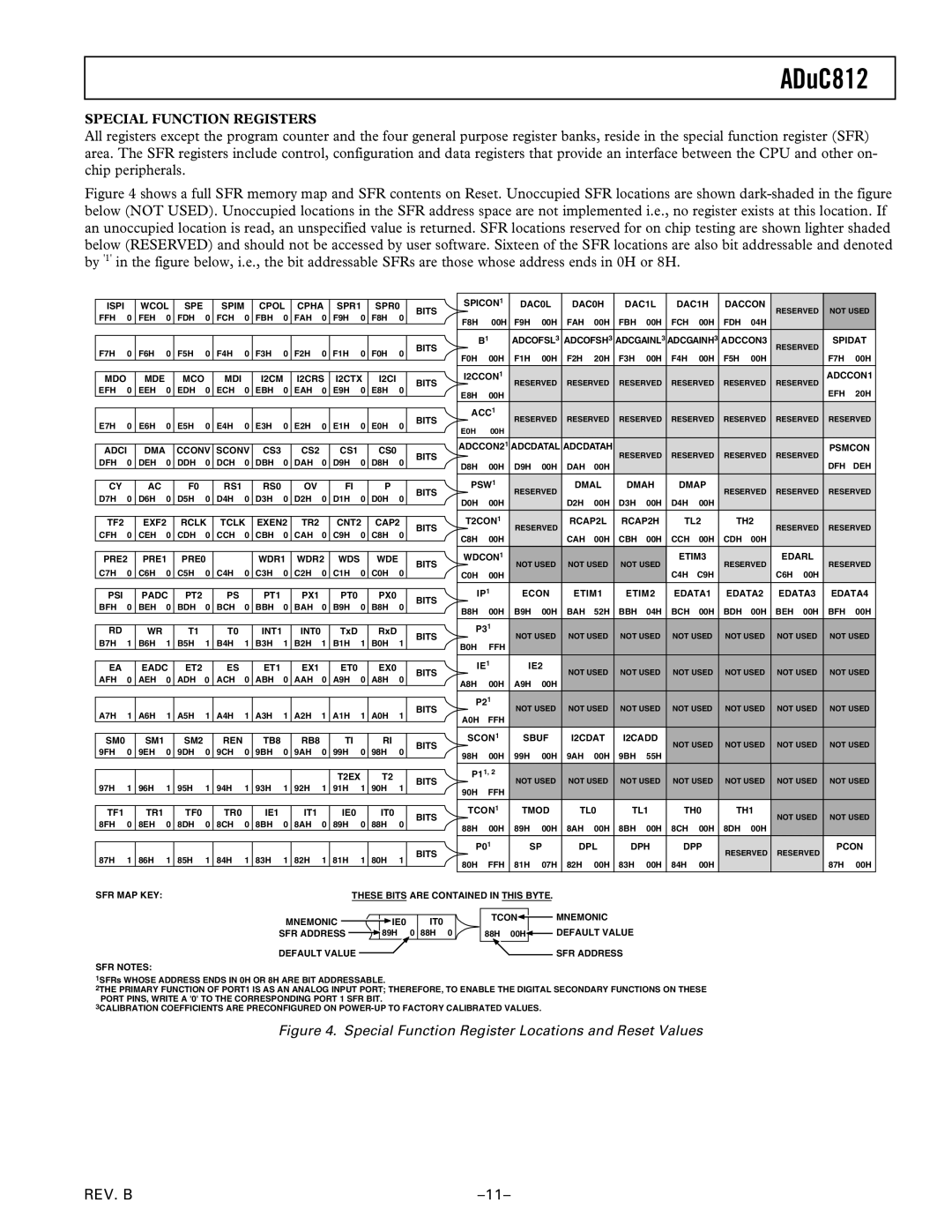

All registers except the program counter and the four general purpose register banks, reside in the special function register (SFR) area. The SFR registers include control, configuration and data registers that provide an interface between the CPU and other on- chip peripherals.

Figure 4 shows a full SFR memory map and SFR contents on Reset. Unoccupied SFR locations are shown dark-shaded in the figure below (NOT USED). Unoccupied locations in the SFR address space are not implemented i.e., no register exists at this location. If an unoccupied location is read, an unspecified value is returned. SFR locations reserved for on chip testing are shown lighter shaded below (RESERVED) and should not be accessed by user software. Sixteen of the SFR locations are also bit addressable and denoted by '1' in the figure below, i.e., the bit addressable SFRs are those whose address ends in 0H or 8H.

ISPI |

|

| WCOL |

| SPE |

|

| SPIM |

|

| CPOL |

| CPHA |

| SPR1 |

| SPR0 |

| BITS | |||||

FFH | 0 |

| FEH | 0 |

| FDH | 0 |

| FCH | 0 |

| FBH | 0 |

| FAH | 0 |

| F9H | 0 |

| F8H | 0 |

| |

|

|

|

|

|

|

|

|

| ||||||||||||||||

F7H | 0 |

| F6H | 0 |

| F5H | 0 |

| F4H | 0 |

| F3H | 0 |

| F2H | 0 |

| F1H | 0 |

| F0H | 0 |

| BITS |

|

|

|

|

|

|

|

| |||||||||||||||||

|

|

|

|

|

|

|

|

| ||||||||||||||||

MDO |

|

| MDE |

|

| MCO |

|

| MDI |

|

| I2CM |

|

| I2CRS |

| I2CTX |

| I2CI |

|

| BITS | ||

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||||

EFH | 0 |

| EEH | 0 |

| EDH | 0 |

| ECH | 0 |

| EBH | 0 |

| EAH | 0 |

| E9H | 0 |

| E8H | 0 |

| |

|

|

|

|

|

|

|

|

| ||||||||||||||||

E7H | 0 |

| E6H | 0 |

| E5H | 0 |

| E4H | 0 |

| E3H | 0 |

| E2H | 0 |

| E1H | 0 |

| E0H | 0 |

| BITS |

|

|

|

|

|

|

|

| |||||||||||||||||

|

|

|

|

|

|

|

|

| ||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||

ADCI |

|

| DMA |

|

| CCONV |

| SCONV |

| CS3 |

|

| CS2 |

|

| CS1 |

|

| CS0 |

|

| BITS | ||

DFH | 0 |

| DEH | 0 |

| DDH | 0 |

| DCH | 0 |

| DBH | 0 |

| DAH | 0 |

| D9H | 0 |

| D8H | 0 |

| |

|

|

|

|

|

|

|

|

| ||||||||||||||||

CY |

|

| AC |

|

| F0 |

|

| RS1 |

|

| RS0 |

|

| OV |

|

| FI |

|

| P |

|

| BITS |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||

D7H | 0 |

| D6H | 0 |

| D5H | 0 |

| D4H | 0 |

| D3H | 0 |

| D2H | 0 |

| D1H | 0 |

| D0H | 0 |

| |

|

|

|

|

|

|

|

|

| ||||||||||||||||

TF2 |

|

| EXF2 |

|

| RCLK |

| TCLK |

| EXEN2 |

| TR2 |

|

| CNT2 |

| CAP2 |

| BITS | |||||

|

|

|

|

|

|

|

|

|

|

| ||||||||||||||

CFH | 0 |

| CEH | 0 |

| CDH | 0 |

| CCH | 0 |

| CBH | 0 |

| CAH | 0 |

| C9H | 0 |

| C8H | 0 |

| |

|

|

|

|

|

|

|

|

| ||||||||||||||||

PRE2 |

| PRE1 |

| PRE0 |

|

|

|

| WDR1 |

| WDR2 |

| WDS |

|

| WDE |

|

| BITS | |||||

|

|

|

|

|

|

|

|

|

|

|

| |||||||||||||

C7H | 0 |

| C6H | 0 |

| C5H | 0 |

| C4H | 0 |

| C3H | 0 |

| C2H | 0 |

| C1H | 0 |

| C0H | 0 |

| |

|

|

|

|

|

|

|

|

| ||||||||||||||||

PSI |

|

| PADC |

| PT2 |

|

| PS |

|

| PT1 |

|

| PX1 |

|

| PT0 |

|

| PX0 |

|

| BITS | |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||||

BFH | 0 |

| BEH | 0 |

| BDH | 0 |

| BCH | 0 |

| BBH | 0 |

| BAH | 0 |

| B9H | 0 |

| B8H | 0 |

| |

|

|

|

|

|

|

|

|

| ||||||||||||||||

RD |

|

| WR |

|

| T1 |

|

| T0 |

|

| INT1 |

|

| INT0 |

|

| TxD |

|

| RxD |

|

| BITS |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||

B7H | 1 |

| B6H | 1 |

| B5H | 1 |

| B4H | 1 |

| B3H | 1 |

| B2H | 1 |

| B1H | 1 |

| B0H | 1 |

| |

|

|

|

|

|

|

|

|

| ||||||||||||||||

EA |

|

| EADC |

| ET2 |

|

| ES |

|

| ET1 |

|

| EX1 |

|

| ET0 |

|

| EX0 |

|

| BITS | |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||||

AFH | 0 |

| AEH | 0 |

| ADH | 0 |

| ACH | 0 |

| ABH | 0 |

| AAH | 0 |

| A9H | 0 |

| A8H | 0 |

| |

|

|

|

|

|

|

|

|

| ||||||||||||||||

A7H | 1 |

| A6H | 1 |

| A5H | 1 |

| A4H | 1 |

| A3H | 1 |

| A2H | 1 |

| A1H | 1 |

| A0H | 1 |

| BITS |

|

|

|

|

|

|

|

| |||||||||||||||||

|

|

|

|

|

|

|

|

| ||||||||||||||||

SM0 |

|

| SM1 |

|

| SM2 |

|

| REN |

|

| TB8 |

|

| RB8 |

|

| TI |

|

| RI |

|

| BITS |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||

9FH | 0 |

| 9EH | 0 |

| 9DH | 0 |

| 9CH | 0 |

| 9BH | 0 |

| 9AH | 0 |

| 99H | 0 |

| 98H | 0 |

| |

|

|

|

|

|

|

|

|

| ||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| T2EX |

|

| T2 |

|

| BITS |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||

97H | 1 |

| 96H | 1 |

| 95H | 1 |

| 94H | 1 |

| 93H | 1 |

| 92H | 1 |

| 91H | 1 |

| 90H | 1 |

| |

|

|

|

|

|

|

|

|

| ||||||||||||||||

TF1 |

|

| TR1 |

|

| TF0 |

|

| TR0 |

|

| IE1 |

|

| IT1 |

|

| IE0 |

|

| IT0 |

|

| BITS |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||

8FH | 0 |

| 8EH | 0 |

| 8DH | 0 |

| 8CH | 0 |

| 8BH | 0 |

| 8AH | 0 |

| 89H | 0 |

| 88H | 0 |

| |

|

|

|

|

|

|

|

|

| ||||||||||||||||

87H | 1 |

| 86H | 1 |

| 85H | 1 |

| 84H | 1 |

| 83H | 1 |

| 82H | 1 |

| 81H | 1 |

| 80H | 1 |

| BITS |

|

|

|

|

|

|

|

| |||||||||||||||||

|

|

|

|

|

|

|

|

| ||||||||||||||||

SPICON1 DAC0L | DAC0H | DAC1L | DAC1H DACCON |

RESERVED NOT USED

F8H | 00H | F9H | 00H | FAH | 00H | FBH | 00H | FCH | 00H | FDH | 04H |

|

|

|

|

B1 | ADCOFSL3 ADCOFSH3 ADCGAINL3 ADCGAINH3 ADCCON3 | RESERVED | SPIDAT | ||||||||||||

F0H 00H F1H 00H F2H 20H | F3H | 00H | F4H | 00H | F5H | 00H |

|

| F7H | 00H | |||||

I2CCON1 | RESERVED | RESERVED | RESERVED | RESERVED | RESERVED | RESERVED | ADCCON1 | ||||||||

|

|

|

| ||||||||||||

E8H | 00H |

|

|

|

|

|

|

|

|

|

|

|

| EFH | 20H |

ACC1 | RESERVED | RESERVED | RESERVED | RESERVED | RESERVED | RESERVED | RESERVED | ||||||||

|

| ||||||||||||||

E0H | 00H |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ADCCON21 ADCDATAL ADCDATAH | RESERVED | RESERVED | RESERVED | RESERVED | PSMCON | ||||||||||

|

|

|

|

|

|

|

| ||||||||

D8H | 00H | D9H | 00H | DAH | 00H |

|

|

|

|

|

|

|

| DFH | DEH |

PSW1 | RESERVED | DMAL | DMAH | DMAP | RESERVED | RESERVED | RESERVED | ||||||||

|

|

|

|

|

|

|

| ||||||||

D0H | 00H |

|

| D2H | 00H | D3H | 00H | D4H | 00H |

|

|

|

|

|

|

T2CON1 | RESERVED | RCAP2L | RCAP2H | TL2 | TH2 | RESERVED | RESERVED | ||||||||

|

|

|

|

|

|

|

|

|

| ||||||

C8H | 00H |

|

| CAH | 00H | CBH | 00H | CCH | 00H | CDH | 00H |

|

|

|

|

WDCON1 | NOT USED | NOT USED | NOT USED | ETIM3 | RESERVED | EDARL | RESERVED | ||||||||

|

|

|

|

|

| ||||||||||

C0H | 00H |

|

|

|

|

|

| C4H | C9H |

|

| C6H | 00H |

|

|

IP1 | ECON | ETIM1 | ETIM2 | EDATA1 | EDATA2 | EDATA3 | EDATA4 | ||||||||

B8H | 00H | B9H | 00H | BAH | 52H | BBH | 04H | BCH | 00H | BDH | 00H | BEH | 00H | BFH | 00H |

P31 | NOT USED | NOT USED | NOT USED | NOT USED | NOT USED | NOT USED | NOT USED | ||||||||

|

| ||||||||||||||

B0H | FFH |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

IE1 | IE2 | NOT USED | NOT USED | NOT USED | NOT USED | NOT USED | NOT USED | ||||||||

|

|

|

| ||||||||||||

A8H | 00H | A9H | 00H |

|

|

|

|

|

|

|

|

|

|

|

|

P21 | NOT USED | NOT USED | NOT USED | NOT USED | NOT USED | NOT USED | NOT USED | ||||||||

|

| ||||||||||||||

A0H | FFH |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

SCON1 | SBUF | I2CDAT | I2CADD | NOT USED | NOT USED | NOT USED | |

|

|

|

| NOT USED | |||

98H | 00H | 99H 00H | 9AH 00H | 9BH 55H |

|

|

|

|

|

|

|

|

|

| |

P11, 2 | NOT USED | NOT USED | NOT USED NOT USED | NOT USED | NOT USED | NOT USED | |

90H | FFH |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

TCON1 | TMOD | TL0 | TL1 | TH0 | TH1 | NOT USED | NOT USED | |||||

|

|

|

|

|

|

|

|

|

|

| ||

88H | 00H | 89H | 00H | 8AH | 00H | 8BH | 00H | 8CH | 00H | 8DH 00H |

|

|

P01 | SP | DPL | DPH | DPP | RESERVED | RESERVED | PCON | |||||

|

|

|

|

|

|

|

|

|

|

| ||

80H | FFH | 81H | 07H | 82H | 00H | 83H | 00H | 84H | 00H |

|

| 87H 00H |

|

|

|

|

|

|

|

|

|

|

|

|

|

SFR MAP KEY: | THESE BITS ARE CONTAINED IN THIS BYTE. |

| ||||||||||

|

|

|

|

|

|

|

| TCON |

|

| MNEMONIC | |

|

|

|

|

|

|

|

| |||||

MNEMONIC |

|

|

|

|

| IE0 | IT0 | |||||

|

|

|

|

|

| |||||||

|

|

|

|

|

|

|

|

| DEFAULT VALUE | |||

SFR ADDRESS |

|

|

| 89H 0 | 88H 0 | 88H 00H |

|

| ||||

|

|

|

| |||||||||

DEFAULT VALUE |

|

|

|

|

| SFR ADDRESS | ||||||

SFR NOTES:

1SFRs WHOSE ADDRESS ENDS IN 0H OR 8H ARE BIT ADDRESSABLE.

2THE PRIMARY FUNCTION OF PORT1 IS AS AN ANALOG INPUT PORT; THEREFORE, TO ENABLE THE DIGITAL SECONDARY FUNCTIONS ON THESE PORT PINS, WRITE A '0' TO THE CORRESPONDING PORT 1 SFR BIT.

3CALIBRATION COEFFICIENTS ARE PRECONFIGURED ON

Figure 4. Special Function Register Locations and Reset Values

REV. B |