|

|

|

| ADuC812 |

| ADuC812BS |

|

| |

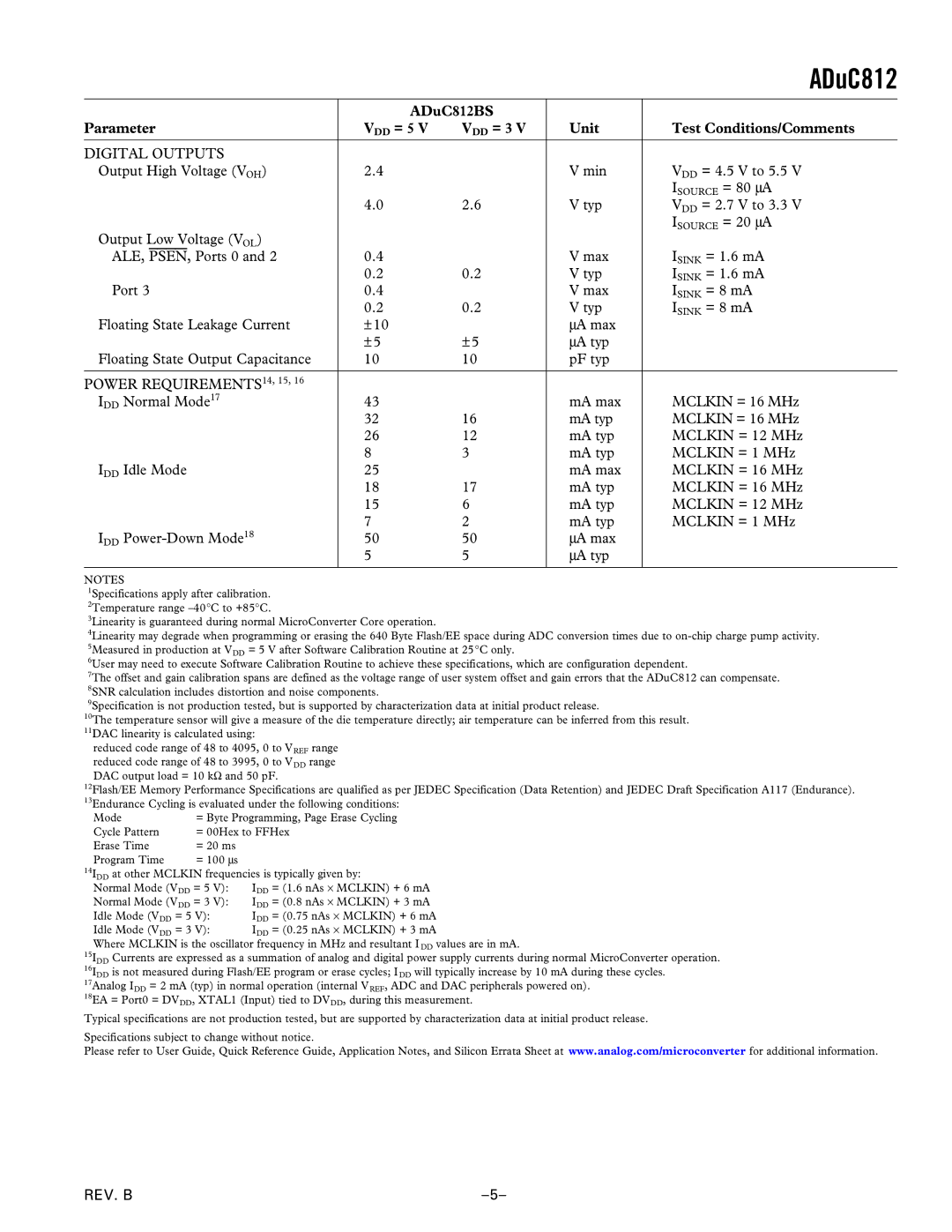

Parameter | VDD = 5 V | VDD = 3 V | Unit | Test Conditions/Comments |

DIGITAL OUTPUTS |

|

|

|

|

Output High Voltage (VOH) | 2.4 |

| V min | VDD = 4.5 V to 5.5 V |

|

|

|

| ISOURCE = 80 ∝A |

| 4.0 | 2.6 | V typ | VDD = 2.7 V to 3.3 V |

Output Low Voltage (VOL) |

|

|

| ISOURCE = 20 ∝A |

|

|

|

| |

ALE, PSEN, Ports 0 and 2 | 0.4 |

| V max | ISINK = 1.6 mA |

| 0.2 | 0.2 | V typ | ISINK = 1.6 mA |

Port 3 | 0.4 |

| V max | ISINK = 8 mA |

| 0.2 | 0.2 | V typ | ISINK = 8 mA |

Floating State Leakage Current | ± 10 |

| ∝A max |

|

| ± 5 | ± 5 | ∝A typ |

|

Floating State Output Capacitance | 10 | 10 | pF typ |

|

|

|

|

|

|

POWER REQUIREMENTS14, 15, 16 |

|

|

|

|

IDD Normal Mode17 | 43 |

| mA max | MCLKIN = 16 MHz |

| 32 | 16 | mA typ | MCLKIN = 16 MHz |

| 26 | 12 | mA typ | MCLKIN = 12 MHz |

| 8 | 3 | mA typ | MCLKIN = 1 MHz |

IDD Idle Mode | 25 |

| mA max | MCLKIN = 16 MHz |

| 18 | 17 | mA typ | MCLKIN = 16 MHz |

| 15 | 6 | mA typ | MCLKIN = 12 MHz |

| 7 | 2 | mA typ | MCLKIN = 1 MHz |

IDD | 50 | 50 | ∝A max |

|

| 5 | 5 | ∝A typ |

|

|

|

|

|

|

NOTES

1Specifications apply after calibration.

2Temperature range

3Linearity is guaranteed during normal MicroConverter Core operation.

4Linearity may degrade when programming or erasing the 640 Byte Flash/EE space during ADC conversion times due to

5Measured in production at VDD = 5 V after Software Calibration Routine at 25°C only.

6User may need to execute Software Calibration Routine to achieve these specifications, which are configuration dependent.

7The offset and gain calibration spans are defined as the voltage range of user system offset and gain errors that the ADuC812 can compensate.

8SNR calculation includes distortion and noise components.

9Specification is not production tested, but is supported by characterization data at initial product release.

10The temperature sensor will give a measure of the die temperature directly; air temperature can be inferred from this result.

11DAC linearity is calculated using:

reduced code range of 48 to 4095, 0 to VREF range reduced code range of 48 to 3995, 0 to VDD range DAC output load = 10 kΩ and 50 pF.

12Flash/EE Memory Performance Specifications are qualified as per JEDEC Specification (Data Retention) and JEDEC Draft Specification A117 (Endurance).

13Endurance Cycling is evaluated under the following conditions:

Mode | = Byte Programming, Page Erase Cycling |

Cycle Pattern | = 00Hex to FFHex |

Erase Time | = 20 ms |

Program Time | = 100 ∝s |

14IDD at other MCLKIN frequencies is typically given by:

Normal Mode (VDD = 5 V): | IDD = (1.6 nAs ⋅ MCLKIN) + 6 mA |

Normal Mode (VDD = 3 V): | IDD = (0.8 nAs ⋅ MCLKIN) + 3 mA |

Idle Mode (VDD = 5 V): | IDD = (0.75 nAs ⋅ MCLKIN) + 6 mA |

Idle Mode (VDD = 3 V): | IDD = (0.25 nAs ⋅ MCLKIN) + 3 mA |

Where MCLKIN is the oscillator frequency in MHz and resultant I DD values are in mA.

15IDD Currents are expressed as a summation of analog and digital power supply currents during normal MicroConverter operation. 16IDD is not measured during Flash/EE program or erase cycles; IDD will typically increase by 10 mA during these cycles.

17Analog IDD = 2 mA (typ) in normal operation (internal VREF, ADC and DAC peripherals powered on).

18EA = Port0 = DVDD, XTAL1 (Input) tied to DVDD, during this measurement.

Typical specifications are not production tested, but are supported by characterization data at initial product release.

Specifications subject to change without notice.

Please refer to User Guide, Quick Reference Guide, Application Notes, and Silicon Errata Sheet at www.analog.com/microconverter for additional information.

REV. B |