ADuC812

Parameter |

|

|

|

|

|

|

|

|

|

|

|

|

|

| Min |

|

| Typ |

|

|

| Max |

|

| Unit | Figure | ||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

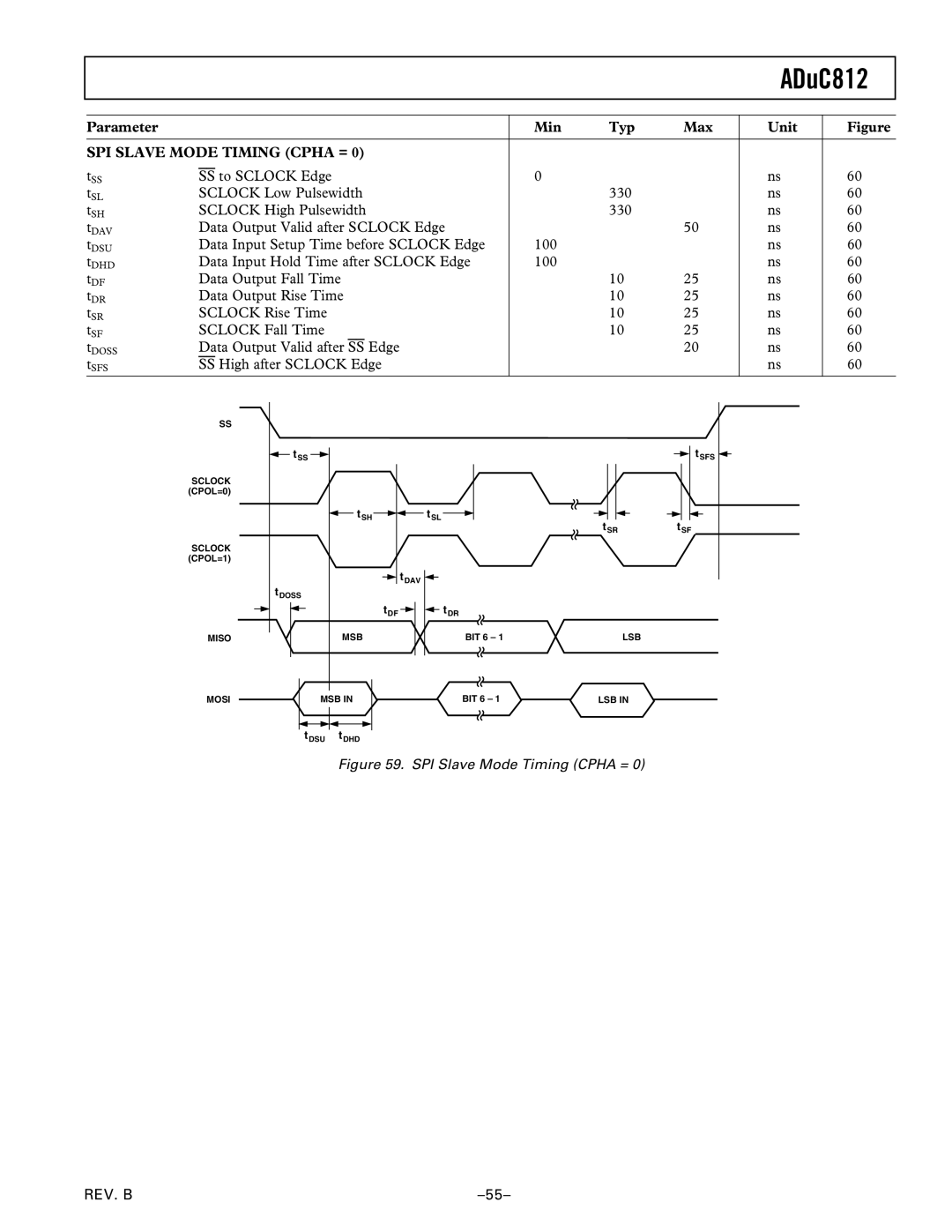

SPI SLAVE MODE TIMING (CPHA = 0) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||

tSS | SS to SCLOCK Edge |

|

|

|

|

| 0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ns | 60 | ||||||||

tSL | SCLOCK Low Pulsewidth |

|

|

|

|

|

|

| 330 |

|

|

|

|

|

|

|

|

| ns | 60 | ||||||||||||

tSH | SCLOCK High Pulsewidth |

|

|

|

|

|

|

| 330 |

|

|

|

|

|

|

|

|

| ns | 60 | ||||||||||||

tDAV | Data Output Valid after SCLOCK Edge |

|

|

|

|

|

|

|

| 50 |

|

| ns | 60 | ||||||||||||||||||

tDSU | Data Input Setup Time before SCLOCK Edge | 100 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ns | 60 | |||||||||||||

tDHD | Data Input Hold Time after SCLOCK Edge | 100 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ns | 60 | |||||||||||||

tDF | Data Output Fall Time |

|

|

|

|

|

|

| 10 |

| 25 |

|

| ns | 60 | |||||||||||||||||

tDR | Data Output Rise Time |

|

|

|

|

|

|

| 10 |

| 25 |

|

| ns | 60 | |||||||||||||||||

tSR | SCLOCK Rise Time |

|

|

|

|

|

|

| 10 |

| 25 |

|

| ns | 60 | |||||||||||||||||

tSF | SCLOCK Fall Time |

|

|

|

|

|

|

| 10 |

| 25 |

|

| ns | 60 | |||||||||||||||||

tDOSS | Data Output Valid after SS Edge |

|

|

|

|

|

|

|

|

|

|

|

|

| 20 |

|

| ns | 60 | |||||||||||||

tSFS | SS High after SCLOCK Edge |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ns | 60 | ||||||||

| SS |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| tSFS |

|

|

|

|

|

|

| tSS |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||

| SCLOCK |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||

| (CPOL=0) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| tSH |

|

|

| tSL |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| tSR |

|

|

| t | SF |

|

|

|

|

|

| |||

| SCLOCK |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||

| (CPOL=1) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||

![]() tDAV

tDAV ![]()

tDOSS

tDF ![]()

![]() tDR

tDR

MISO

MSB

BIT 6 – 1 | LSB |

MOSI

MSB IN

BIT 6 – 1 | LSB IN |

tDSU tDHD

Figure 59. SPI Slave Mode Timing (CPHA = 0)

REV. B |