ADuC812

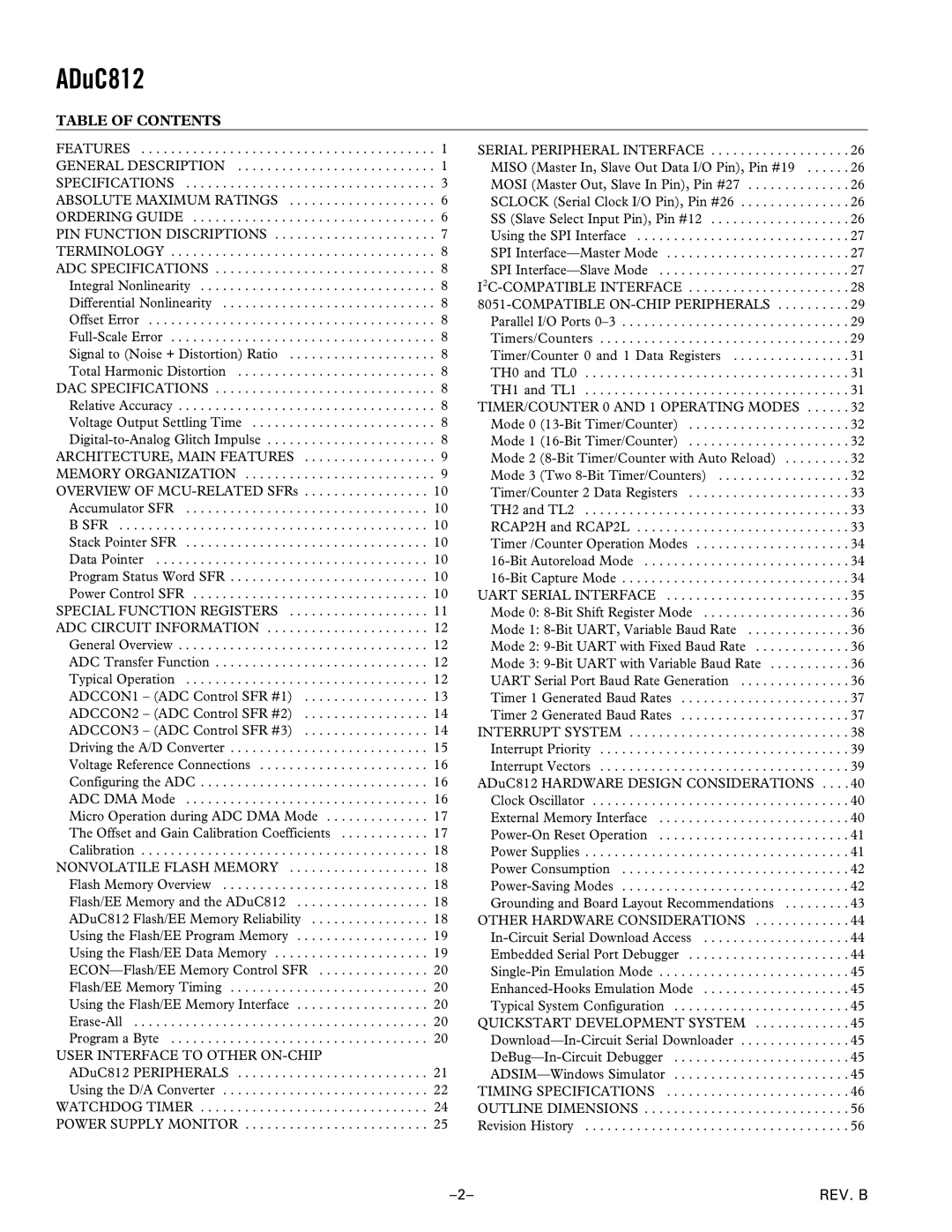

TABLE OF CONTENTS

FEATURES | . 1 |

GENERAL DESCRIPTION | . 1 |

SPECIFICATIONS | . 3 |

ABSOLUTE MAXIMUM RATINGS | . 6 |

ORDERING GUIDE | . 6 |

PIN FUNCTION DISCRIPTIONS | . 7 |

TERMINOLOGY | . 8 |

ADC SPECIFICATIONS | . 8 |

Integral Nonlinearity | . 8 |

Differential Nonlinearity | . 8 |

Offset Error | . 8 |

. 8 | |

Signal to (Noise + Distortion) Ratio | . 8 |

Total Harmonic Distortion | . 8 |

DAC SPECIFICATIONS | . 8 |

Relative Accuracy | . 8 |

Voltage Output Settling Time | . 8 |

. 8 | |

ARCHITECTURE, MAIN FEATURES | . 9 |

MEMORY ORGANIZATION | . 9 |

OVERVIEW OF | 10 |

Accumulator SFR | 10 |

B SFR | 10 |

Stack Pointer SFR | 10 |

Data Pointer | 10 |

Program Status Word SFR | 10 |

Power Control SFR | 10 |

SPECIAL FUNCTION REGISTERS | 11 |

ADC CIRCUIT INFORMATION | 12 |

General Overview | 12 |

ADC Transfer Function | 12 |

Typical Operation | 12 |

ADCCON1 – (ADC Control SFR #1) | 13 |

ADCCON2 – (ADC Control SFR #2) | 14 |

ADCCON3 – (ADC Control SFR #3) | 14 |

Driving the A/D Converter | 15 |

Voltage Reference Connections | 16 |

Configuring the ADC | 16 |

ADC DMA Mode | 16 |

Micro Operation during ADC DMA Mode | 17 |

The Offset and Gain Calibration Coefficients | 17 |

Calibration | 18 |

NONVOLATILE FLASH MEMORY | 18 |

Flash Memory Overview | 18 |

Flash/EE Memory and the ADuC812 | 18 |

ADuC812 Flash/EE Memory Reliability | 18 |

Using the Flash/EE Program Memory | 19 |

Using the Flash/EE Data Memory | 19 |

20 | |

Flash/EE Memory Timing | 20 |

Using the Flash/EE Memory Interface | 20 |

20 | |

Program a Byte | 20 |

USER INTERFACE TO OTHER |

|

ADuC812 PERIPHERALS | 21 |

Using the D/A Converter | 22 |

WATCHDOG TIMER | 24 |

POWER SUPPLY MONITOR | 25 |

SERIAL PERIPHERAL INTERFACE | 26 |

MISO (Master In, Slave Out Data I/O Pin), Pin #19 | 26 |

MOSI (Master Out, Slave In Pin), Pin #27 | 26 |

SCLOCK (Serial Clock I/O Pin), Pin #26 | 26 |

SS (Slave Select Input Pin), Pin #12 | 26 |

Using the SPI Interface | 27 |

SPI | 27 |

SPI | 27 |

28 | |

29 | |

Parallel I/O Ports | 29 |

Timers/Counters | 29 |

Timer/Counter 0 and 1 Data Registers | 31 |

TH0 and TL0 | 31 |

TH1 and TL1 | 31 |

TIMER/COUNTER 0 AND 1 OPERATING MODES | 32 |

Mode 0 | 32 |

Mode 1 | 32 |

Mode 2 | 32 |

Mode 3 (Two | 32 |

Timer/Counter 2 Data Registers | 33 |

TH2 and TL2 | 33 |

RCAP2H and RCAP2L | 33 |

Timer /Counter Operation Modes | 34 |

34 | |

34 | |

UART SERIAL INTERFACE | 35 |

Mode 0: | 36 |

Mode 1: | 36 |

Mode 2: | 36 |

Mode 3: | 36 |

UART Serial Port Baud Rate Generation | 36 |

Timer 1 Generated Baud Rates | 37 |

Timer 2 Generated Baud Rates | 37 |

INTERRUPT SYSTEM | 38 |

Interrupt Priority | 39 |

Interrupt Vectors | 39 |

ADuC812 HARDWARE DESIGN CONSIDERATIONS . . . . 40 | |

Clock Oscillator | 40 |

External Memory Interface | 40 |

41 | |

Power Supplies | 41 |

Power Consumption | 42 |

42 | |

Grounding and Board Layout Recommendations | 43 |

OTHER HARDWARE CONSIDERATIONS | 44 |

44 | |

Embedded Serial Port Debugger | 44 |

45 | |

45 | |

Typical System Configuration | 45 |

QUICKSTART DEVELOPMENT SYSTEM | 45 |

45 | |

45 | |

45 | |

TIMING SPECIFICATIONS | 46 |

OUTLINE DIMENSIONS | 56 |

Revision History | 56 |

REV. B |