ADuC812

|

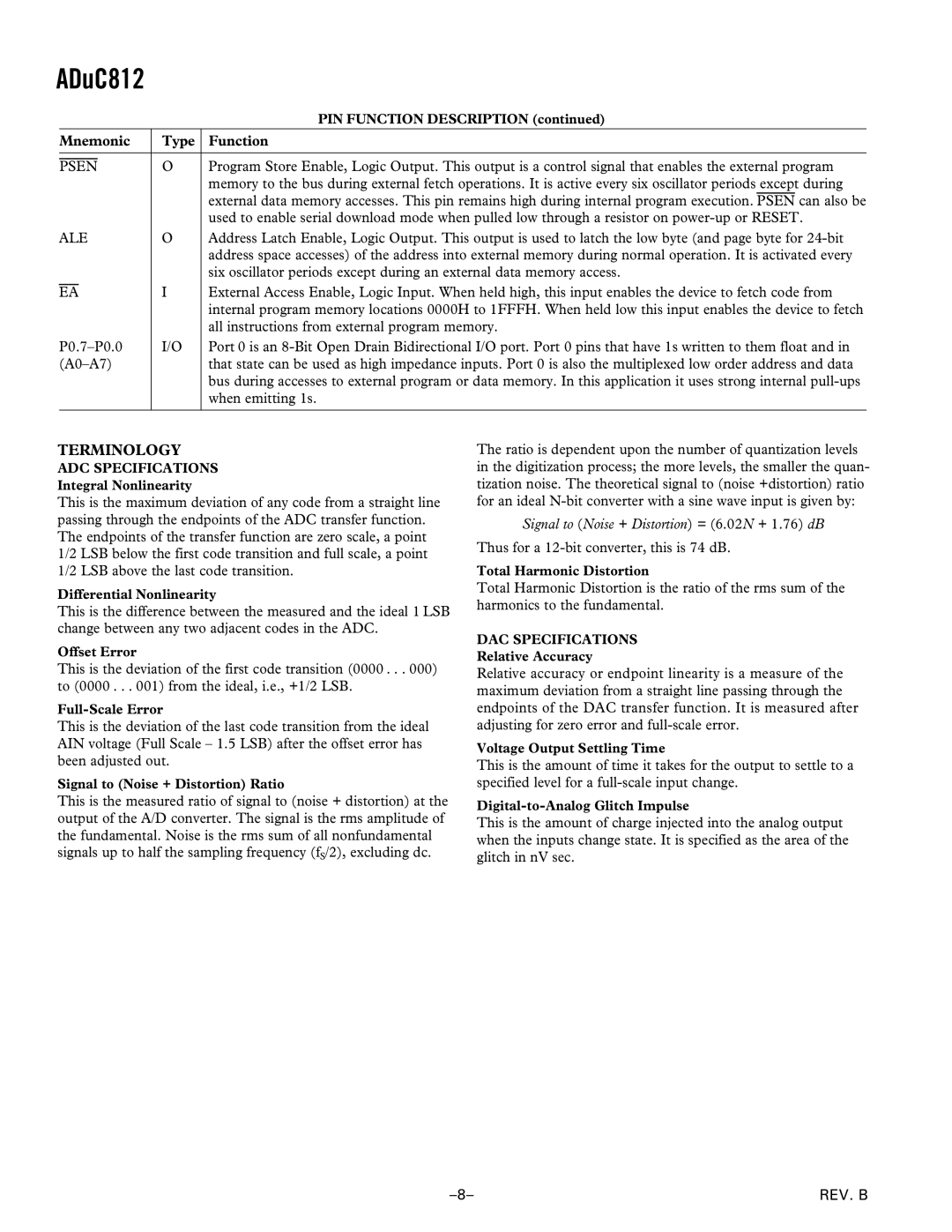

| PIN FUNCTION DESCRIPTION (continued) |

Mnemonic | Type | Function |

|

|

|

PSEN | O | Program Store Enable, Logic Output. This output is a control signal that enables the external program |

|

| memory to the bus during external fetch operations. It is active every six oscillator periods except during |

|

| external data memory accesses. This pin remains high during internal program execution. PSEN can also be |

|

| used to enable serial download mode when pulled low through a resistor on |

ALE | O | Address Latch Enable, Logic Output. This output is used to latch the low byte (and page byte for |

|

| address space accesses) of the address into external memory during normal operation. It is activated every |

|

| six oscillator periods except during an external data memory access. |

EA | I | External Access Enable, Logic Input. When held high, this input enables the device to fetch code from |

|

| internal program memory locations 0000H to 1FFFH. When held low this input enables the device to fetch |

|

| all instructions from external program memory. |

I/O | Port 0 is an | |

| that state can be used as high impedance inputs. Port 0 is also the multiplexed low order address and data | |

|

| bus during accesses to external program or data memory. In this application it uses strong internal |

|

| when emitting 1s. |

|

|

|

TERMINOLOGY

ADC SPECIFICATIONS

Integral Nonlinearity

This is the maximum deviation of any code from a straight line passing through the endpoints of the ADC transfer function. The endpoints of the transfer function are zero scale, a point 1/2 LSB below the first code transition and full scale, a point 1/2 LSB above the last code transition.

Differential Nonlinearity

This is the difference between the measured and the ideal 1 LSB change between any two adjacent codes in the ADC.

Offset Error

This is the deviation of the first code transition (0000 . . . 000) to (0000 . . . 001) from the ideal, i.e., +1/2 LSB.

This is the deviation of the last code transition from the ideal AIN voltage (Full Scale – 1.5 LSB) after the offset error has been adjusted out.

Signal to (Noise + Distortion) Ratio

This is the measured ratio of signal to (noise + distortion) at the output of the A/D converter. The signal is the rms amplitude of the fundamental. Noise is the rms sum of all nonfundamental signals up to half the sampling frequency (fS/2), excluding dc.

The ratio is dependent upon the number of quantization levels in the digitization process; the more levels, the smaller the quan- tization noise. The theoretical signal to (noise +distortion) ratio for an ideal

Signal to (Noise + Distortion) = (6.02N + 1.76) dB

Thus for a 12-bit converter, this is 74 dB.

Total Harmonic Distortion

Total Harmonic Distortion is the ratio of the rms sum of the harmonics to the fundamental.

DAC SPECIFICATIONS

Relative Accuracy

Relative accuracy or endpoint linearity is a measure of the maximum deviation from a straight line passing through the endpoints of the DAC transfer function. It is measured after adjusting for zero error and

Voltage Output Settling Time

This is the amount of time it takes for the output to settle to a specified level for a

This is the amount of charge injected into the analog output when the inputs change state. It is specified as the area of the glitch in nV sec.

REV. B |