ADuC812

|

| 12 MHz | Variable Clock |

|

| ||

Parameter |

| Min | Max | Min | Max | Unit | Figure |

|

|

|

|

|

|

| |

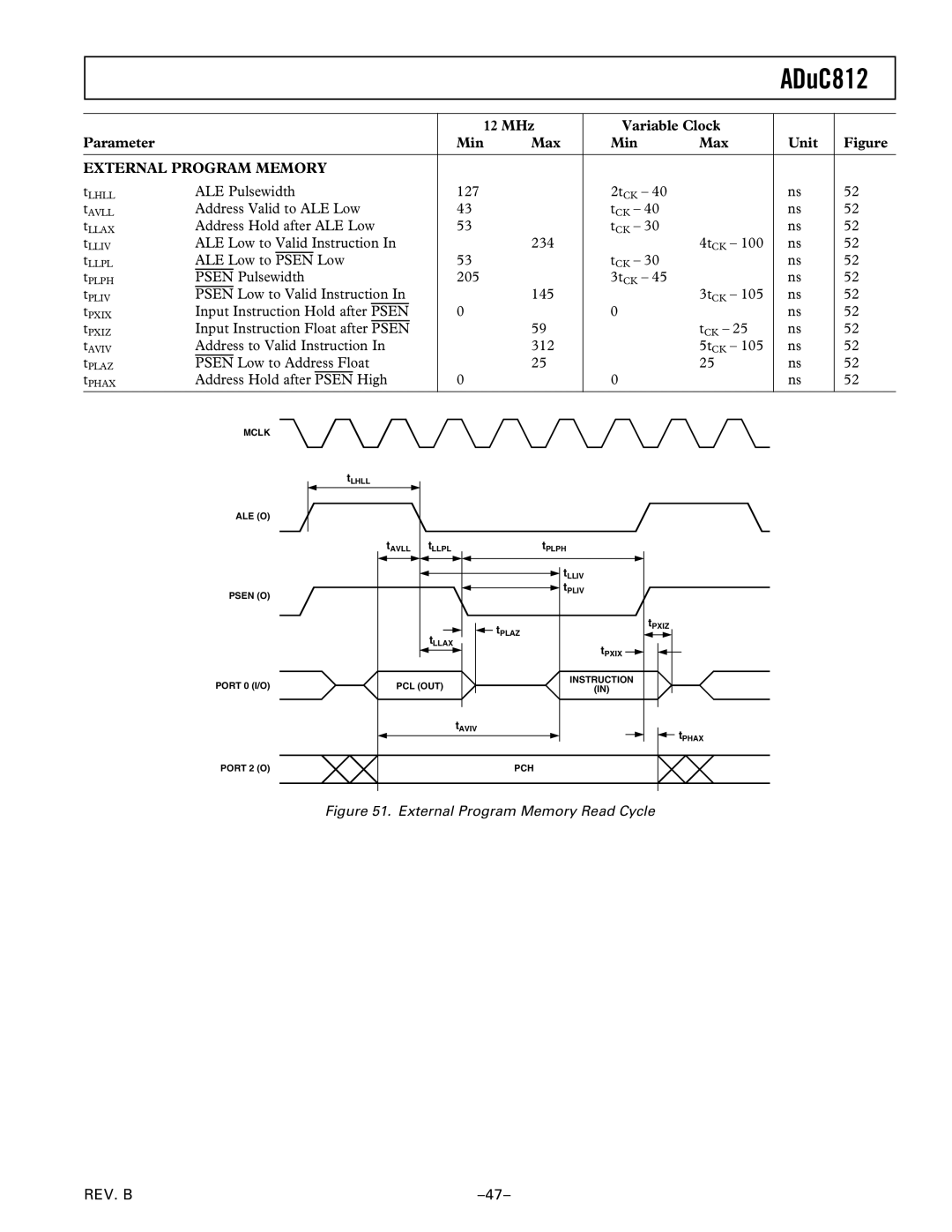

EXTERNAL PROGRAM MEMORY |

|

|

|

|

|

| |

tLHLL | ALE Pulsewidth | 127 |

| 2tCK – 40 |

| ns | 52 |

tAVLL | Address Valid to ALE Low | 43 |

| tCK – 40 |

| ns | 52 |

tLLAX | Address Hold after ALE Low | 53 |

| tCK – 30 |

| ns | 52 |

tLLIV | ALE Low to Valid Instruction In |

| 234 |

| 4tCK – 100 | ns | 52 |

tLLPL | ALE Low to PSEN Low | 53 |

| tCK – 30 |

| ns | 52 |

tPLPH | PSEN Pulsewidth | 205 |

| 3tCK – 45 |

| ns | 52 |

tPLIV | PSEN Low to Valid Instruction In |

| 145 |

| 3tCK – 105 | ns | 52 |

tPXIX | Input Instruction Hold after PSEN | 0 |

| 0 |

| ns | 52 |

tPXIZ | Input Instruction Float after PSEN |

| 59 |

| tCK – 25 | ns | 52 |

tAVIV | Address to Valid Instruction In |

| 312 |

| 5tCK – 105 | ns | 52 |

tPLAZ | PSEN Low to Address Float |

| 25 |

| 25 | ns | 52 |

tPHAX | Address Hold after PSEN High | 0 |

| 0 |

| ns | 52 |

MCLK

| tLHLL |

|

| |

ALE (O) |

|

|

| |

| tAVLL | tLLPL | tPLPH | |

|

|

| tLLIV | |

PSEN (O) |

|

| tPLIV | |

|

|

| ||

|

|

| tPXIZ | |

|

| tLLAX | tPLAZ | |

|

| tPXIX | ||

|

|

| ||

PORT 0 (I/O) | PCL (OUT) | INSTRUCTION | ||

(IN) | ||||

|

|

| ||

|

|

| tAVIV | |

|

|

| tPHAX | |

PORT 2 (O) |

|

| PCH | |

Figure 51. External Program Memory Read Cycle

REV. B |