ADuC812

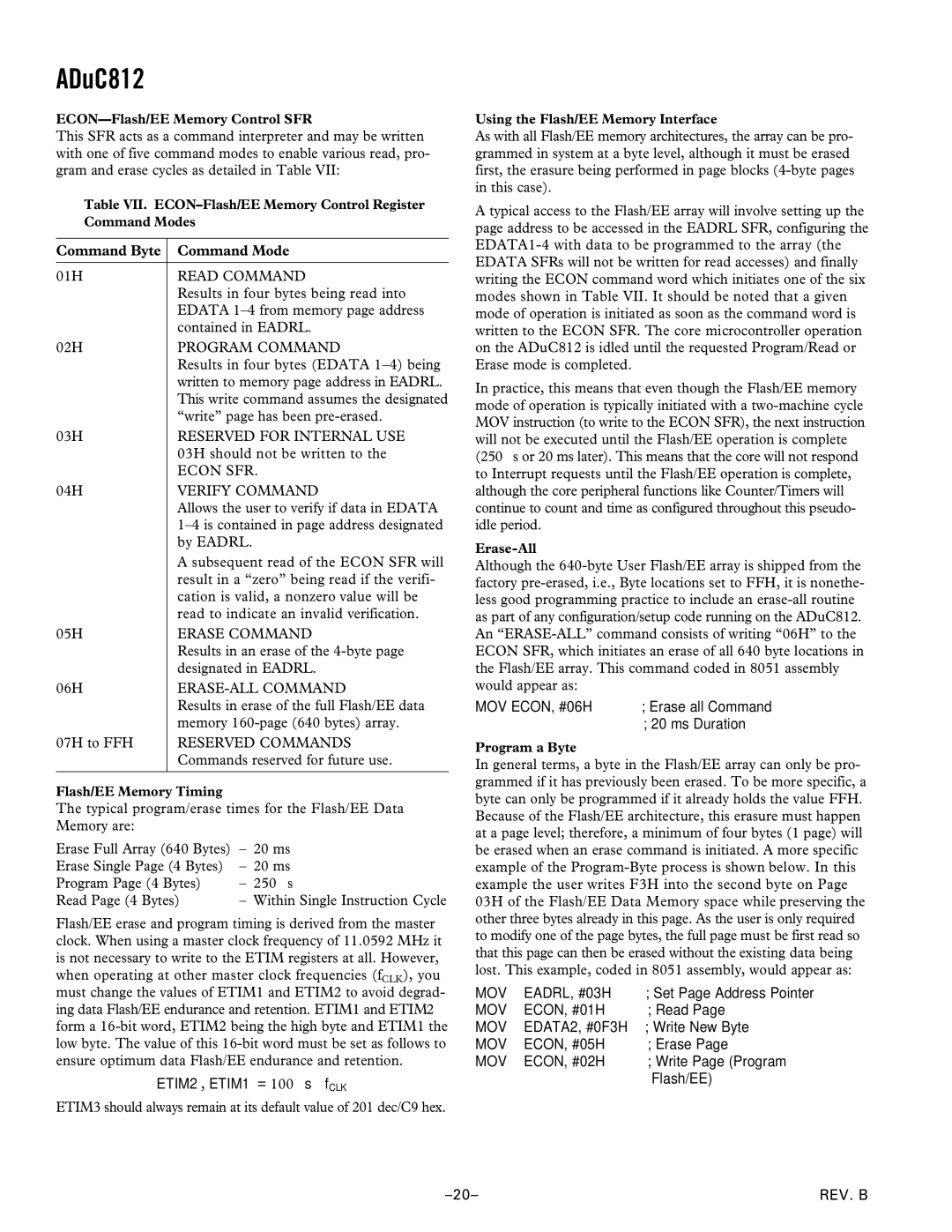

This SFR acts as a command interpreter and may be written with one of five command modes to enable various read, pro- gram and erase cycles as detailed in Table VII:

Table VII.

Command Byte | Command Mode |

|

|

01H | READ COMMAND |

| Results in four bytes being read into |

| EDATA |

| contained in EADRL. |

02H | PROGRAM COMMAND |

| Results in four bytes (EDATA |

| written to memory page address in EADRL. |

| This write command assumes the designated |

| “write” page has been |

03H | RESERVED FOR INTERNAL USE |

| 03H should not be written to the |

| ECON SFR. |

04H | VERIFY COMMAND |

| Allows the user to verify if data in EDATA |

| |

| by EADRL. |

| A subsequent read of the ECON SFR will |

| result in a “zero” being read if the verifi- |

| cation is valid, a nonzero value will be |

| read to indicate an invalid verification. |

05H | ERASE COMMAND |

| Results in an erase of the |

| designated in EADRL. |

06H | |

| Results in erase of the full Flash/EE data |

| memory |

07H to FFH | RESERVED COMMANDS |

| Commands reserved for future use. |

|

|

Flash/EE Memory Timing

The typical program/erase times for the Flash/EE Data Memory are:

Erase Full Array (640 Bytes) | – 20 ms | |

Erase Single Page (4 Bytes) | – 20 ms | |

Program Page (4 Bytes) | – | 250 ∝s |

Read Page (4 Bytes) | – | Within Single Instruction Cycle |

Flash/EE erase and program timing is derived from the master clock. When using a master clock frequency of 11.0592 MHz it is not necessary to write to the ETIM registers at all. However, when operating at other master clock frequencies (fCLK), you must change the values of ETIM1 and ETIM2 to avoid degrad- ing data Flash/EE endurance and retention. ETIM1 and ETIM2 form a

ETIM2, ETIM1 = 100 ∝s ⋅ fCLK

ETIM3 should always remain at its default value of 201 dec/C9 hex.

Using the Flash/EE Memory Interface

As with all Flash/EE memory architectures, the array can be pro- grammed in system at a byte level, although it must be erased first, the erasure being performed in page blocks

A typical access to the Flash/EE array will involve setting up the page address to be accessed in the EADRL SFR, configuring the

In practice, this means that even though the Flash/EE memory mode of operation is typically initiated with a

Although the

MOV ECON, #06H | ; Erase all Command |

| ; 20 ms Duration |

Program a Byte

In general terms, a byte in the Flash/EE array can only be pro- grammed if it has previously been erased. To be more specific, a byte can only be programmed if it already holds the value FFH. Because of the Flash/EE architecture, this erasure must happen at a page level; therefore, a minimum of four bytes (1 page) will be erased when an erase command is initiated. A more specific example of the

MOV | EADRL, #03H | ; Set Page Address Pointer |

MOV | ECON, #01H | ; Read Page |

MOV | EDATA2, #0F3H | ; Write New Byte |

MOV | ECON, #05H | ; Erase Page |

MOV | ECON, #02H | ; Write Page (Program |

|

| Flash/EE) |

REV. B |