ADuC812

WATCHDOG TIMER

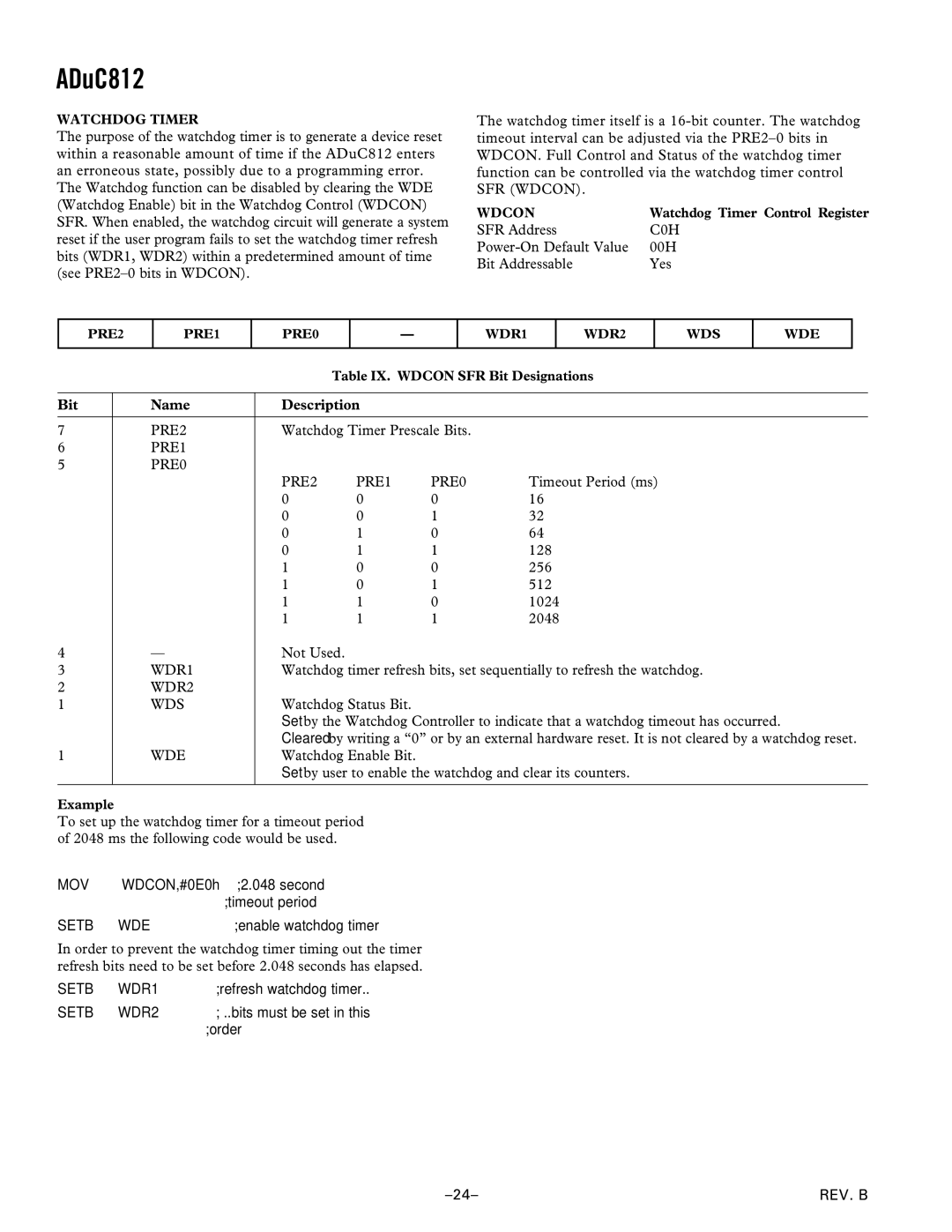

The purpose of the watchdog timer is to generate a device reset within a reasonable amount of time if the ADuC812 enters an erroneous state, possibly due to a programming error.

The Watchdog function can be disabled by clearing the WDE (Watchdog Enable) bit in the Watchdog Control (WDCON) SFR. When enabled, the watchdog circuit will generate a system reset if the user program fails to set the watchdog timer refresh bits (WDR1, WDR2) within a predetermined amount of time (see

The watchdog timer itself is a

WDCON | Watchdog Timer Control Register |

SFR Address | C0H |

00H | |

Bit Addressable | Yes |

PRE2

PRE1

PRE0

—

WDR1

WDR2

WDS

WDE

Table IX. WDCON SFR Bit Designations

Bit | Name | Description |

|

| |

|

|

|

| ||

7 | PRE2 | Watchdog Timer Prescale Bits. |

| ||

6 | PRE1 |

|

|

|

|

5 | PRE0 |

|

|

|

|

|

| PRE2 | PRE1 | PRE0 | Timeout Period (ms) |

|

| 0 | 0 | 0 | 16 |

|

| 0 | 0 | 1 | 32 |

|

| 0 | 1 | 0 | 64 |

|

| 0 | 1 | 1 | 128 |

|

| 1 | 0 | 0 | 256 |

|

| 1 | 0 | 1 | 512 |

|

| 1 | 1 | 0 | 1024 |

|

| 1 | 1 | 1 | 2048 |

4 | — | Not Used. |

|

|

|

3 | WDR1 | Watchdog timer refresh bits, set sequentially to refresh the watchdog. | |||

2 | WDR2 |

|

|

|

|

1 | WDS | Watchdog Status Bit. |

|

| |

|

| Set by the Watchdog Controller to indicate that a watchdog timeout has occurred. | |||

|

| Cleared by writing a “0” or by an external hardware reset. It is not cleared by a watchdog reset. | |||

1 | WDE | Watchdog Enable Bit. |

|

| |

|

| Set by user to enable the watchdog and clear its counters. | |||

|

|

|

|

|

|

Example

To set up the watchdog timer for a timeout period of 2048 ms the following code would be used.

MOV | WDCON,#0E0h | ;2.048 second |

|

| ;timeout period |

SETB | WDE | ;enable watchdog timer |

In order to prevent the watchdog timer timing out the timer refresh bits need to be set before 2.048 seconds has elapsed.

SETB | WDR1 | ;refresh watchdog timer.. |

SETB | WDR2 | ; ..bits must be set in this |

|

| ;order |

REV. B |