ADuC812

|

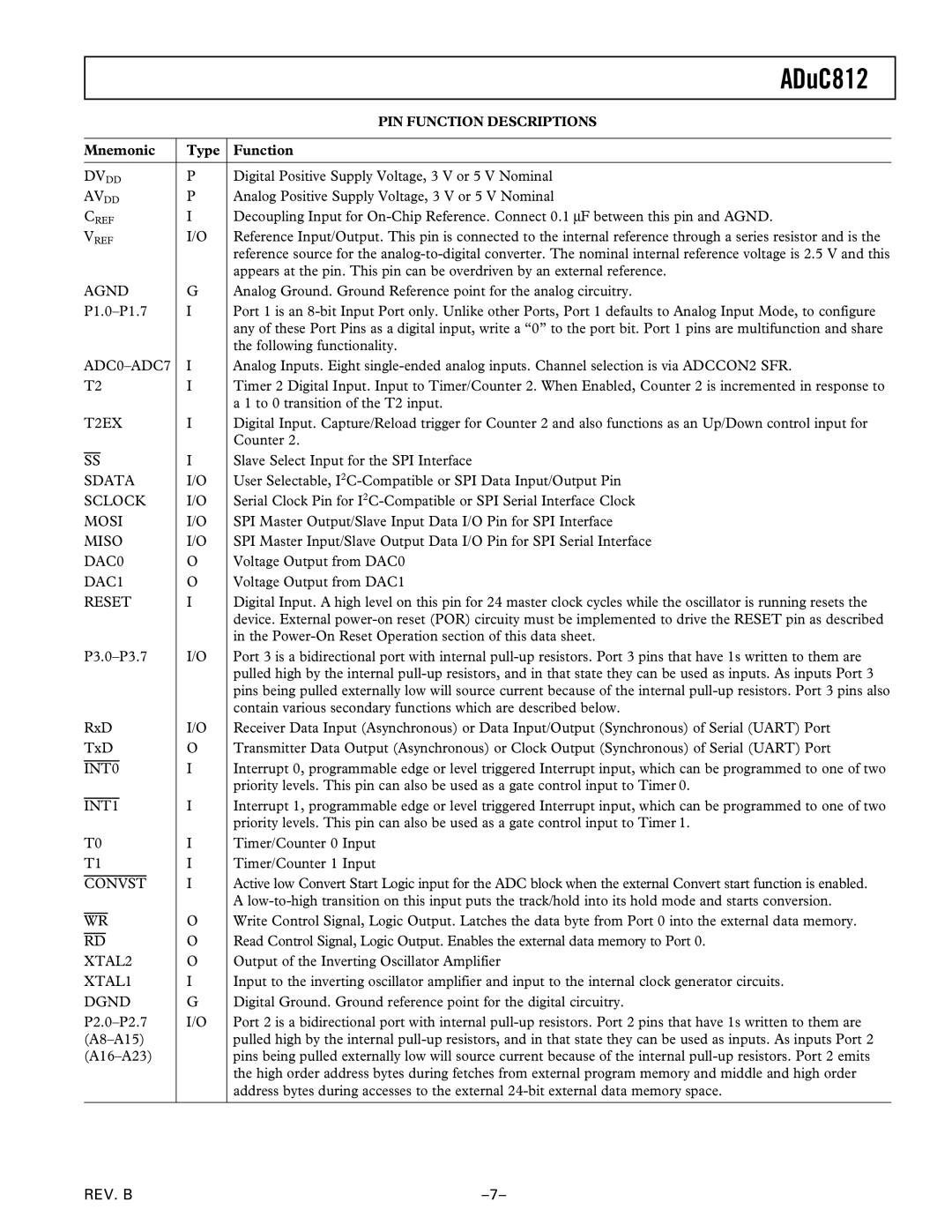

| PIN FUNCTION DESCRIPTIONS |

|

|

|

Mnemonic | Type | Function |

|

|

|

DVDD | P | Digital Positive Supply Voltage, 3 V or 5 V Nominal |

AVDD | P | Analog Positive Supply Voltage, 3 V or 5 V Nominal |

CREF | I | Decoupling Input for |

VREF | I/O | Reference Input/Output. This pin is connected to the internal reference through a series resistor and is the |

|

| reference source for the |

|

| appears at the pin. This pin can be overdriven by an external reference. |

AGND | G | Analog Ground. Ground Reference point for the analog circuitry. |

I | Port 1 is an | |

|

| any of these Port Pins as a digital input, write a “0” to the port bit. Port 1 pins are multifunction and share |

|

| the following functionality. |

| I | Analog Inputs. Eight |

T2 | I | Timer 2 Digital Input. Input to Timer/Counter 2. When Enabled, Counter 2 is incremented in response to |

|

| a 1 to 0 transition of the T2 input. |

T2EX | I | Digital Input. Capture/Reload trigger for Counter 2 and also functions as an Up/Down control input for |

|

| Counter 2. |

SSI Slave Select Input for the SPI Interface

SDATA | I/O | User Selectable, |

SCLOCK | I/O | Serial Clock Pin for |

MOSI | I/O | SPI Master Output/Slave Input Data I/O Pin for SPI Interface |

MISO | I/O | SPI Master Input/Slave Output Data I/O Pin for SPI Serial Interface |

DAC0 | O | Voltage Output from DAC0 |

DAC1 | O | Voltage Output from DAC1 |

RESET | I | Digital Input. A high level on this pin for 24 master clock cycles while the oscillator is running resets the |

|

| device. External |

|

| in the |

I/O | Port 3 is a bidirectional port with internal | |

|

| pulled high by the internal |

|

| pins being pulled externally low will source current because of the internal |

|

| contain various secondary functions which are described below. |

RxD | I/O | Receiver Data Input (Asynchronous) or Data Input/Output (Synchronous) of Serial (UART) Port |

TxD | O | Transmitter Data Output (Asynchronous) or Clock Output (Synchronous) of Serial (UART) Port |

INT0 | I | Interrupt 0, programmable edge or level triggered Interrupt input, which can be programmed to one of two |

|

| priority levels. This pin can also be used as a gate control input to Timer 0. |

INT1 | I | Interrupt 1, programmable edge or level triggered Interrupt input, which can be programmed to one of two |

|

| priority levels. This pin can also be used as a gate control input to Timer 1. |

T0 | I | Timer/Counter 0 Input |

T1 | I | Timer/Counter 1 Input |

CONVST | I | Active low Convert Start Logic input for the ADC block when the external Convert start function is enabled. |

|

| A |

WR | O | Write Control Signal, Logic Output. Latches the data byte from Port 0 into the external data memory. |

RD | O | Read Control Signal, Logic Output. Enables the external data memory to Port 0. |

XTAL2 | O | Output of the Inverting Oscillator Amplifier |

XTAL1 | I | Input to the inverting oscillator amplifier and input to the internal clock generator circuits. |

DGND | G | Digital Ground. Ground reference point for the digital circuitry. |

I/O | Port 2 is a bidirectional port with internal | |

| pulled high by the internal | |

| pins being pulled externally low will source current because of the internal | |

|

| the high order address bytes during fetches from external program memory and middle and high order |

|

| address bytes during accesses to the external |

REV. B |