ADuC812

Timer 1 Generated Baud Rates

When Timer 1 is used as the baud rate generator, the baud rates in Modes 1 and 3 are determined by the Timer 1 overflow rate and the value of SMOD as follows:

Modes 1 and 3 Baud Rate =

(2SMOD/32) ⋅ (Timer 1 Overflow Rate)

The Timer 1 interrupt should be disabled in this application. The Timer itself can be configured for either timer or counter opera- tion, and in any of its three running modes. In the most typical application, it is configured for timer operation, in the Autoreload mode (high nibble of TMOD = 0010 Binary). In that case, the baud rate is given by the formula:

Modes 1 and 3 Baud Rate = (2SMOD/32) ⋅ (Core Clock/(12 ⋅

Table XXI shows some

Table XXI.

Ideal | Core | SMOD | Actual | % | |

Baud | CLK | Value | Value | Baud | Error |

|

|

|

|

|

|

9600 | 12 | 1 | 8929 | 7 | |

19200 | 11.0592 | 1 | 19200 | 0 | |

9600 | 11.0592 | 0 | 9600 | 0 | |

2400 | 11.0592 | 0 | 2400 | 0 | |

|

|

|

|

|

|

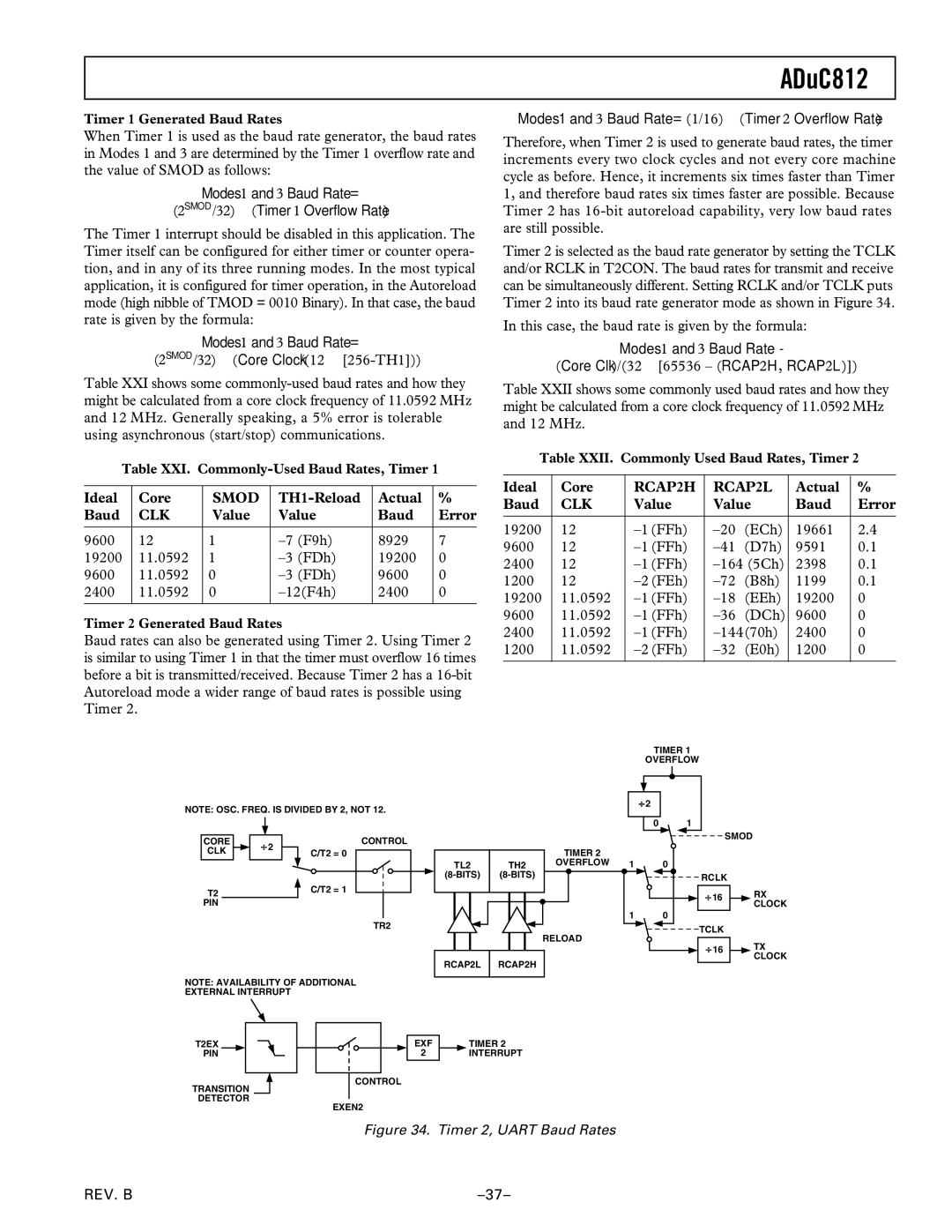

Timer 2 Generated Baud Rates

Baud rates can also be generated using Timer 2. Using Timer 2 is similar to using Timer 1 in that the timer must overflow 16 times before a bit is transmitted/received. Because Timer 2 has a

Modes 1 and 3 Baud Rate = (1/16) ⋅ (Timer 2 Overflow Rate)

Therefore, when Timer 2 is used to generate baud rates, the timer increments every two clock cycles and not every core machine cycle as before. Hence, it increments six times faster than Timer 1, and therefore baud rates six times faster are possible. Because Timer 2 has

Timer 2 is selected as the baud rate generator by setting the TCLK and/or RCLK in T2CON. The baud rates for transmit and receive can be simultaneously different. Setting RCLK and/or TCLK puts Timer 2 into its baud rate generator mode as shown in Figure 34.

In this case, the baud rate is given by the formula:

Modes 1 and 3 Baud Rate -

(Core Clk)/(32 ⋅ [65536 – (RCAP2H, RCAP2L)])

Table XXII shows some commonly used baud rates and how they might be calculated from a core clock frequency of 11.0592 MHz and 12 MHz.

Table XXII. Commonly Used Baud Rates, Timer 2

Ideal | Core | RCAP2H | RCAP2L | Actual | % | |

Baud | CLK | Value | Value | Baud | Error | |

|

|

|

|

|

|

|

19200 | 12 | (ECh) | 19661 | 2.4 | ||

9600 | 12 | (D7h) | 9591 | 0.1 | ||

2400 | 12 | 2398 | 0.1 | |||

1200 | 12 | (B8h) | 1199 | 0.1 | ||

19200 | 11.0592 | (EEh) | 19200 | 0 | ||

9600 | 11.0592 | (DCh) | 9600 | 0 | ||

2400 | 11.0592 | 2400 | 0 | |||

1200 | 11.0592 | (E0h) | 1200 | 0 | ||

|

|

|

|

|

|

|

NOTE: OSC. FREQ. IS DIVIDED BY 2, NOT 12.

CORE | 2 | CONTROL |

TIMER 1

OVERFLOW

2 |

|

0 | 1 |

SMOD

CLK | C/T2 = 0 |

T2 | C/T2 = 1 |

| |

PIN |

|

| TR2 |

NOTE: AVAILABILITY OF ADDITIONAL | |

EXTERNAL INTERRUPT |

|

|

| TIMER 2 |

|

TL2 | TH2 | OVERFLOW 1 | 0 |

|

| ||

|

| 1 | 0 |

|

| RELOAD |

|

RCAP2L | RCAP2H |

|

|

RCLK

![]() 16

16

TCLK

![]() 16

16

RX CLOCK

TX CLOCK

T2EX | EXF |

PIN | 2 |

CONTROL

TRANSITION

DETECTOR

EXEN2

TIMER 2 INTERRUPT

Figure 34. Timer 2, UART Baud Rates

REV. B |