Delta DOP Series HMI Connection ManualDOP-A/AE/AS Series

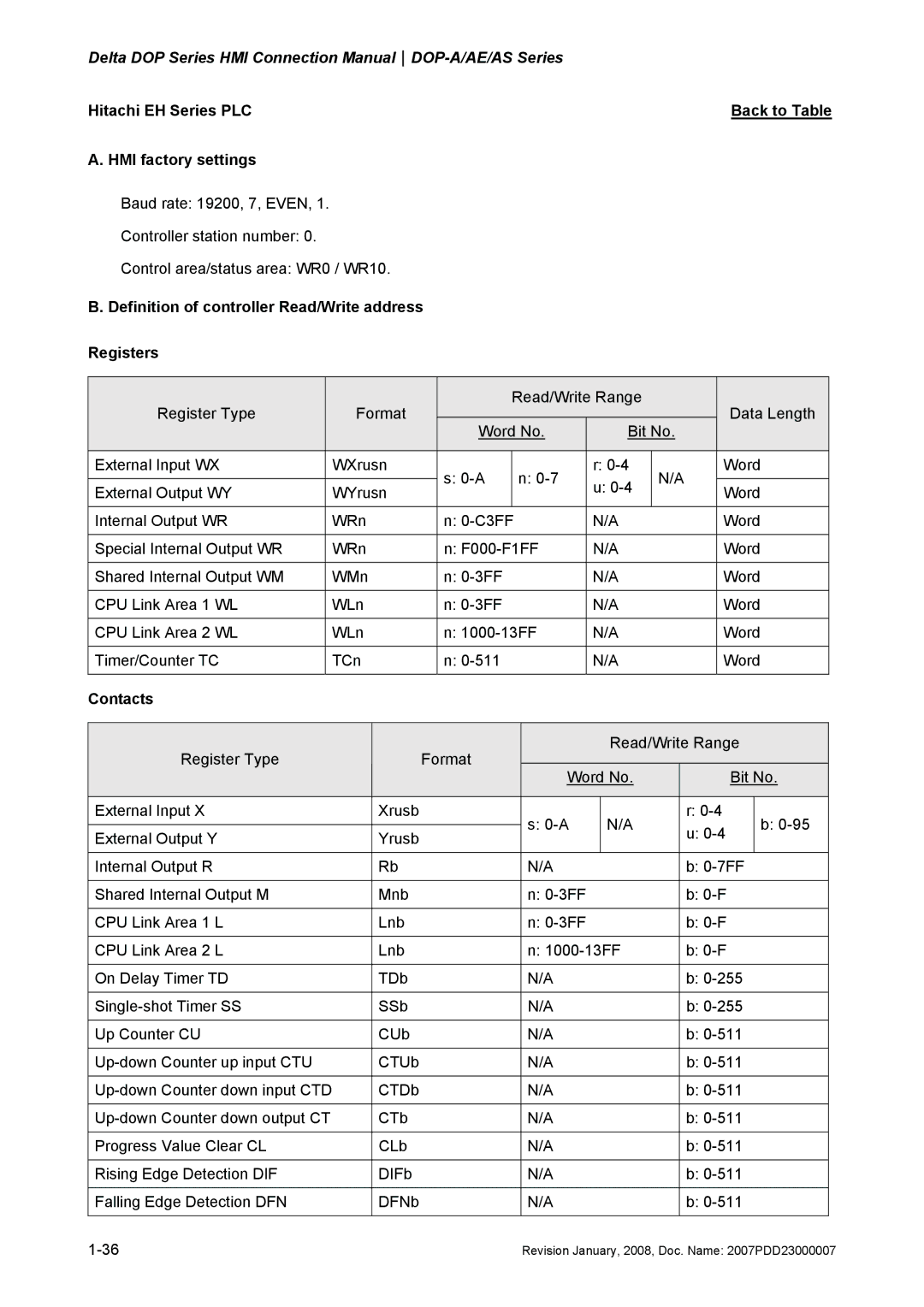

Hitachi EH Series PLCBack to Table A. HMI factory settings

Baud rate: 19200, 7, EVEN, 1.

Controller station number: 0.

Control area/status area: WR0 / WR10.

B. Definition of controller Read/Write address

Registers

Register Type |

| Format |

|

| Read/Write Range |

|

| Data Length |

| ||||||

|

|

|

|

|

|

|

|

|

| ||||||

|

| Word No. |

| Bit No. | |||||||||||

|

|

|

|

|

|

|

|

|

| ||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

External Input WX |

| WXrusn |

| s: | n: | r: | N/A | Word |

| ||||||

|

|

|

|

| u: |

|

|

|

| ||||||

External Output WY |

| WYrusn |

|

|

|

|

| ||||||||

|

|

|

|

|

|

| Word |

|

| ||||||

|

|

|

|

|

|

|

|

|

|

| |||||

Internal Output WR |

| WRn |

|

| n: | N/A |

|

| Word |

|

| ||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Special Internal Output WR |

| WRn |

|

| n: | N/A |

|

| Word |

|

| ||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Shared Internal Output WM |

| WMn |

|

| n: |

|

| N/A |

|

| Word |

|

| ||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

CPU Link Area 1 WL |

| WLn |

|

| n: |

|

| N/A |

|

| Word |

|

| ||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

CPU Link Area 2 WL |

| WLn |

|

| n: | N/A |

|

| Word |

|

| ||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Timer/Counter TC |

| TCn |

|

| n: |

|

| N/A |

|

| Word |

|

| ||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Contacts |

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

Register Type |

|

| Format |

|

|

| Read/Write Range |

|

| ||||||

|

|

|

|

|

|

|

|

|

|

|

| ||||

|

|

| Word No. |

|

| Bit No. |

| ||||||||

|

|

|

|

|

|

|

|

|

| ||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

External Input X |

| Xrusb |

|

|

| s: |

| N/A |

| r: |

| b: |

| ||

|

|

|

|

|

|

|

|

| u: |

|

| ||||

External Output Y |

| Yrusb |

|

|

|

|

| ||||||||

|

|

|

|

|

|

|

|

|

|

| |||||

|

|

|

|

|

|

|

|

|

|

|

|

| |||

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

Internal Output R |

| Rb |

|

|

| N/A |

|

|

| b: |

|

| |||

|

|

|

|

|

|

|

|

|

|

|

|

| |||

Shared Internal Output M |

| Mnb |

|

|

| n: |

|

|

| b: |

|

| |||

|

|

|

|

|

|

|

|

|

|

|

|

| |||

CPU Link Area 1 L |

| Lnb |

|

|

| n: |

|

|

| b: |

|

| |||

|

|

|

|

|

|

|

|

|

|

| |||||

CPU Link Area 2 L |

| Lnb |

|

|

| n: |

| b: |

|

| |||||

|

|

|

|

|

|

|

|

|

|

|

|

| |||

On Delay Timer TD |

| TDb |

|

|

| N/A |

|

|

| b: |

|

| |||

|

|

|

|

|

|

|

|

|

|

|

|

| |||

| SSb |

|

|

| N/A |

|

|

| b: |

|

| ||||

|

|

|

|

|

|

|

|

|

|

|

|

| |||

Up Counter CU |

| CUb |

|

|

| N/A |

|

|

| b: |

|

| |||

|

|

|

|

|

|

|

|

|

|

|

|

| |||

| CTUb |

|

|

| N/A |

|

|

| b: |

|

| ||||

|

|

|

|

|

|

|

|

|

|

|

| ||||

CTDb |

|

|

| N/A |

|

|

| b: |

|

| |||||

|

|

|

|

|

|

|

|

|

|

|

|

| |||

| CTb |

|

|

| N/A |

|

|

| b: |

|

| ||||

|

|

|

|

|

|

|

|

|

|

|

|

| |||

Progress Value Clear CL |

| CLb |

|

|

| N/A |

|

|

| b: |

|

| |||

|

|

|

|

|

|

|

|

|

|

|

|

| |||

Rising Edge Detection DIF |

| DIFb |

|

|

| N/A |

|

|

| b: |

|

| |||

|

|

|

|

|

|

|

|

|

|

|

|

| |||

Falling Edge Detection DFN |

| DFNb |

|

|

| N/A |

|

|

| b: |

|

| |||

|

|

|

|

|

|

|

|

|

| ||||||

|

|

|

|

|

| Revision January, 2008, Doc. Name: 2007PDD23000007 | |||||||||