DMC-1700/1800

Using This Manual

1X80 17X8

Contents

Connecting Hardware

Ii Contents

Programming Motion

Iv Contents

Application Programming 135

Troubleshooting 181

Vi Contents

Introduction

DMC-1700/1800 Overview

Standard Servo Motor with +/- 10 Volt Command Signal

Stepper Motor with Step and Direction Signals

Overview of Motor Types

DMC-1700/1800 Functional Elements

Microcomputer Section

Motor Interface

Communication

General I/O

System Elements

Motor

Amplifier Driver

Encoder

Watch Dog Timer

This page Left Blank Intentionally

DMC-17x0 and DMC-18x0 Motion Controllers

DMC-1700/1800 Getting Started

RAM

JP1 JP3

Elements You Need

JP5

JP6

JP8

Installing the DMC-1700/1800

Determine Overall Motor Configuration

Standard Servo Motor Operation

Sinusoidal Commutation

Install Jumpers on the DMC-1700/1800

Optional IRQ Interrupt Jumpers

Optional Motor Off Jumpers

Install the Communications Software

Install the DMC-1700/1800 in the PC

DMC-1700 Install

DMC-1800 Install

Using Galil Software for DOS DMC-1700 only

Using Galil Software for Windows 98 SE, ME, XP,

On the first dialog, select Add/Troubleshoot

DMC-1700/1800 Getting Started

Getting Started

Automatically Assigned resources in Win 98 SE

Device Manager in Win 98 SE

Edit Input/Output Range in Win 98 SE

Using Galil Software for Windows NT

DMC-1700/1800 Getting Started

Sending Test Commands to the Terminal

Determine the Axes to be Used for Sinusoidal Commutation

Make Connections to Amplifier and Encoder

Getting Started

Connect Standard Servo Motors

Check the Polarity of the Feedback Loop

Inverting the Loop Polarity

BGX CR

DC Power Supply

Getting Started

Connect Sinusoidal Commutation Motors

Baxz

If Hall Sensors are Available

If Hall Sensors are Not Available

Connect Step Motors

AMX

Tune the Servo System

TE X CR

Design Examples

Example 1 System Set-up

Example 2 Profiled Move

Instruction Interpretation

Example 5 Position Interrogation

Example 3 Multiple Axes

Example 4 Independent Moves

Example 8 Operation Under Torque Limit

Example 6 Absolute Position

Example 7 Velocity Control

Example 10 Operation in the Buffer Mode

Example 11 Using the On-Board Editor

Example 9 Interrogation

Line # Instruction Interpretation

Example 12 Motion Programs with Loops

Example 13 Motion Programs with Trippoints

Example 14 Control Variables

BGY

Example 15 Linear Interpolation

Example 16 Circular Interpolation

4000

This page Left Blank Intentionally

Using Optoisolated Inputs

Limit Switch Input

DMC-1700/1800 Connecting Hardware

Overview

Home Switch Input

Abort Input

Wiring the Optoisolated Inputs

Uncommitted Digital Inputs

Using an Isolated Power Supply

Optoisolated Inputs

Bypassing the Opto-Isolation

Analog Inputs

Amplifier Interface

TTL Inputs

TTL Outputs

DMC-1700/1800 Connecting Hardware

This page Left Blank Intentionally

Software Tools and Communications

DMC-1700/1800 Software Tools and Communications

DMC-1800 FIFO, DPRAM, IRQ DMC-1700 FIFO, DMA, IRQ

Galil SmartTERM

Galil SmartTERM

Recent enough to support the QU command

DMC Program Editor Window

Data Record Display for a DMC-1840

Galil Registry Editor

Communication Settings for ISA and PCI

Setting Communications Parameters and Methods

General Communications Parameters Dialog

Stall Thread and Delay Thread Methods

Interrupt Communications Method

Data Record Cache Depth

Data Record Refresh Rate

DMC-1700 Data Record Parameters

Windows Servo Design Kit Wsdk

Wsdk Main Screen

Creating Custom Software Interfaces

Galil Communications API with C/C++

Sending Commands in VB

Declare Functions

End Sub

Enabling Event Interrupts EI command

DOS, Linux, and QNX tools

Controller Event Interrupts and User Interrupts

Linux

Bit Number Condition

Bit number Input

Status Byte hex Condition

Hardware Level Communications for ISA and PCI

Communications with the DMC-1700

Simplified Communications Procedure

Communication with DMC-1700

Control Register N+1

Register Address Read/Write Description

Interrupt Service for the DMC-1700

Reading the Data Record using the Polling Fifo

Determining the Base Address

Polling Fifo Mode Read Procedure

Secondary Fifo Registers

Simplified Communication Procedure

PCI Device Identification

Read, Write, and Control Registers

Communication with DMC-1800

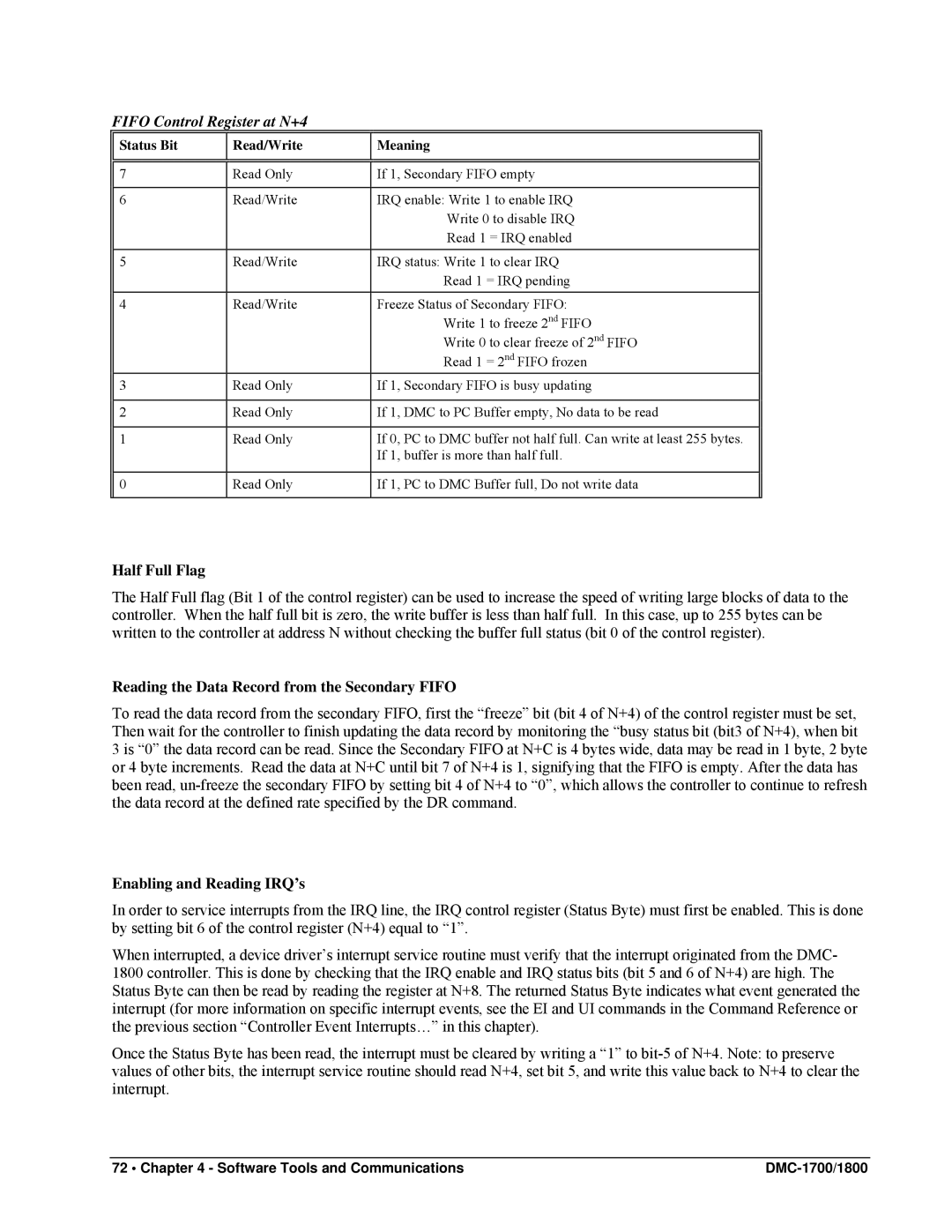

Fifo Control Register at N+4

Half Full Flag

Reading the Data Record from the Secondary Fifo

Enabling and Reading IRQ’s

Reset Register at N+8

Dual Port RAM Dpram access for reading the Data Record

DMA / Secondary Fifo / Dpram Memory Map

Write

General output block 6 outputs

DMC-1700/1800 Software Tools and Communications

Axis Switch Information 1 Byte

General Status Information 1 Byte

Axis Status Information 1 Word

BIT

DMC-1700/1800 Software Tools and Communications

This page Left Blank Intentionally

Command Syntax Ascii

DMC-1700/1800 Command Basics

Command Syntax Binary

Coordinated Motion with more than 1 axis

Binary Command Format

Header Format

Datafields Format

A7 02 00 05 03 E8 FE 0C

Binary command table

Example

Interrogation Commands

Summary of Interrogation Commands

Controller Response to Data

Interrogating the Controller

Operands

Interrogating Current Commanded Values

Command Summary

DMC-1700/1800 Programming Motion

VS,VA,VD

Operand Summary Independent Axis

Command Summary Independent Axis

Independent Axis Positioning

Example Absolute Position Movement

Example Multiple Move Sequence

Command Summary Jogging

Command

Independent Jogging

Axis velocity profile

Example Joystick Jogging

Position Tracking

Example Jog in X only

Command Description PT1

Example Motion

Position vs Time msec Motion

Velocity vs Time msec Motion

Trip Points

Velocity vs.Time Motion

Linear Interpolation Mode

Command Summary Position Tracking Mode

Command Description

Specifying Linear Segments

Specifying Vector Speed for Each Segment

Additional Commands

An Example of Linear Interpolation Motion

Command Summary Linear Interpolation

Operand Summary Linear Interpolation

Changing Feedrate

LM?

Example Linear Move

LM ZW

COUNT=0

Example Multiple Moves

#LOAD

Specifying Vector Segments

Vector Mode Linear and Circular Interpolation Motion

Specifying the Coordinate Plane

Additional commands

Tangent Motion

Compensating for Differences in Encoder Resolution

Trippoints

Example

Command Summary Coordinated Motion Sequence

Operand Summary Coordinated Motion Sequence

Electronic Gearing

Required Path

Ramped Gearing

GA Z, Z

Example Electronic Gearing Over a Specified Interval

MO Z

Command Summary Electronic Gearing

Example Gantry Mode

Example Simple Master Slave

Example Electronic Gearing

GA,X

Electronic Cam

GA, CX

ET0=,0

EM 6000,1500

EP 2000,0

EG x,y,z,w

EQ x,y,z,w

Command Summary Electronic CAM

Command Description

Operand Summary Electronic CAM

Example Electronic CAM

Contour Mode

Specifying Contour Segments

CMX

DT0CD0

Command Summary Contour Mode

Command CM Xyzw CM Abcdefgh

General Velocity Profiles

Generating an Array An Example

Contour Mode Example

#POINTS

POSC=V4

DIFC=POSD-POSC

Teach Record and Play-Back

Record and Playback Example

Virtual Axis

Ecam Master Example

Sinusoidal Motion Example

DT2

Monitoring Generated Pulses vs Commanded Pulses

Stepper Motor Operation

Specifying Stepper Motor Operation

Stepper Motor Smoothing

Using an Encoder with Stepper Motors

Command Summary Stepper Motor Operation

Operand Summary Stepper Motor Operation

Motion Complete Trippoint

Stepper Position Maintenance Mode SPM

Error Limit

Internal Controller Commands user can query

User Configurable Commands user can query & change

Example SPM Mode Setup

Correction

Full-Stepping Drive, X axis

Half-Stepping Drive, X axis

Example Error Correction

#MOTION

#LOOPJP#LOOP

#POSERR

Example Friction Correction

Using the CE Command

Additional Commands for the Auxiliary Encoder

Dual Loop Auxiliary Encoder

DE 0,500,-30,300

Backlash Compensation

Continuous Dual Loop Example

Sampled Dual Loop Example

V1= DEX

Using the IT and VT Commands

Motion Smoothing

Example Smoothing

JP#END,@ABSV22

Using the KS Command Step Motor Smoothing

Trapezoidal velocity and smooth velocity profiles

Homing

Stage

MG AT Home

Example Homing

#HOME

Switch

Command Summary Homing Operation

High Speed Position Capture The Latch Function

Operand Summary Homing Operation

Example Find Edge

Fast Update Rate Mode

AL Y

Programming Motion

DMC-1700/1800 Application Programming

Using the DMC-1700/1800 Editor to Enter Programs

ED #BEGIN

Program Format

Edit Mode Commands

Using Labels in Programs

Commenting Programs

Using the command, no or Apostrophe ‘

Special Labels

HX n

Executing Programs Multitasking

XQ #A, n

Trace Commands

Error Code Command

Stop Code Command

RAM Memory Interrogation Commands

Debugging Example

Program Flow Commands

Operands

Event Triggers & Trippoints

Function

DMC-1700 and DMC-1800 Event Triggers

AS X Y Z W S

Event Trigger Examples

Event Trigger Multiple Move Sequence

Event Trigger Set Output after Distance

Event Trigger Repetitive Position Trigger

Event Trigger Change Speed along Vector Path

Event Trigger Set output when At speed

Event Trigger Start Motion on Input

Event Trigger Multiple Move with Wait

Define Output Waveform Using AT

Conditional Jumps

Command Format JP and JS

Logical operators

Conditional Statements

Multiple Conditional Statements

Using If, Else, and Endif Commands

Using the JP Command

Example Using JP command

Using the if and Endif Commands

Using the Else Command

Command Format IF, Else and Endif

Example using IF, Else and Endif

Nesting if Conditional Statements

Subroutines

Stack Manipulation

Auto-Start Routine

Automatic Subroutines for Monitoring Conditions

Example Limit Switch

Example Position Error

Example Motion Complete Timeout

Example Input Interrupt

Example Command Error

Example Command Error w/Multitasking

Bit-Wise Operators

Mathematical and Functional Expressions

Mathematical Operators

Functions

ENTER,LENS6

FLEN=@FRACLEN

LEN1=FLEN&$00FF

Variables

Programmable Variables

Assigning Values to Variables

PR Posx

Example Using Variables for Joystick

Operands

Assigning Variable Values to Controller Parameters

Displaying the value of variables at the terminal

Arrays

Special Operands Keywords

Defining Arrays

Examples of Internal Variables

Uploading and Downloading Arrays to On Board Memory

Using a Variable to Address Array Elements

Assignment of Array Entries

Data Types for Recording

Command Summary Automatic Data Capture

Automatic Data Capture into Arrays

Input of Data

Input of Data Numeric and String

Deallocating Array Space

Output of Data Numeric and String

Sending Messages

Cut-to-Length Example

Inputting String Variables

Final Value is

Using the MG Command to Configure Terminals

Formatting Messages

MG 07

Displaying Variables and Arrays

Summary of Message Functions

Local Formatting of Response of Interrogation Commands

PF m.n

LZ0

LZ1

Formatting Variables and Array Elements

Converting to User Units

Local Formatting of Variables

VF m.n

Hardware I/O

Digital Outputs

Example Start Motion on Switch

Digital Inputs

Input Interrupt Function

AI 1BGX

Example Position Follower Point-to-Point

Analog Inputs

Examples Input Interrupt

Wire Cutter

Example Applications

Example Position Follower Continuous Move

VER=VAR-TPX

JP #A

Table Controller

Inch = 40,000 counts

CR 80000,270,-360

BGZ

AMZ

BGZ AMZ

Speed Control by Joystick

Speed = 20000 x VIN

Position Control by Joystick

Backlash Compensation by Sampled Dual-Loop

JG VEL JP #B

DP0

Instruction

This page Left Blank Intentionally

Hardware Protection

Output Protection Lines

Input Protection Lines

DMC-1700/1800 Hardware & Software Protection

Signal or Function State if Error Occurs

Software Protection

Programmable Position Limits

# Poserr

Off-On-Error

Automatic Error Routine

Limit Switch Routine

#AJP #AEN

JP#END

#LF

Stxamx

#LR MG Reverse Limit

Installation

DMC-1700/1800 Troubleshooting

Communication

Stability

Operation

This page Left Blank Intentionally

Theory of Operation

DMC-1700/1800 Theory of Operation

Level

Operation of Closed-Loop Systems

Velocity and Position Profiles

System Modeling

Functional Elements of a Motion Control System

Motor-Amplifier

Voltage Drive

Current Drive

= 2 Ω

Velocity Loop

T1 = J/Ka Kt Kg

Voltage Source

DAC

Digital Filter

Amp

System Analysis

Motor

Dz = 1030 z-0.95/Z

Encoder

Digital Filter

System Design and Compensation

Analytical Method

= 76 180 6 =

PM = 180 + α =

Kd = 10/32768 =

= 4 ∗ KP

KP =

Equivalent Filter Form DMC-1700/1800

Electrical Specifications

Servo Control

Stepper Control

Input/Output

Performance Specifications

Power

Connectors for DMC-1700/1800 Main Board

J1 DMC-1740/1840 A-D Axes Main J5-DMC-1740/1840 A-D Axes

J8 DMC-1780/1880 J6 DMC-1780/1880 J7 DMC-1780/1880

Axes Main PIN IDC Auxiliary Encoder

Pin-Out Description for DMC-1700/1800

Outputs

PWM/STEP OUT

Inputs

HEX JPR A8 JPR A7 JPR A6 JPR A5 JPR A4 JPR A3 JPR A2

Setting Addresses for the DMC-1700

Standard Addresses

2AC

2BC

2CC

2DC

3CC

3AC

3BC

Plug and Play Addresses

Communications Jumpers

Accessories and Options

PC/AT Interrupts and Their Vectors

ICM-1900 Interconnect Module

Terminal Label Description

Mocmdx

Signx

Pwmx

GND +VCC

AN2

AN3

AN4

AN5

AMP-19X0 Mating Power Amplifiers

Features

Specifications

ICM-1900 Drawing

OUT GND

ICM-2900 Interconnect Module

OUT PWR

ANA GND

ANALOG5

ANALOG6

ANALOG7

MBX

Standard Opto-isolation and High Current Opto-isolation

Opto-Isolated Outputs ICM-1900 / ICM-2900 -Opto option

Extended I/O of the DMC-17x8/1700/1800 Controller

Accessing extended I/O

Saving the State of the Outputs in Non-Volatile Memory

CO n

OP m,a,b,c,d

MG @IN17

Connector Description

OP 7,,,,7

GND

J8 50-PIN IDC

IOM-1964 Opto-Isolation Module for Extended I/O Controllers

Description

Overview

Buffer chips

Configuring Hardware Banks

Figure A.4 CB-50-80 and CB-50-100 Bracket Layout

Figure A.5 IOM-1964 Chip Configuration Layout

Input Circuit

Sinking Sourcing

High Power Digital Outputs

Figure A.9 High Current Output Circuit

Internal Pullup

Output Command Result

Standard Digital Outputs

Electrical Specifications

High Power Digital Outputs

Digital Inputs

Standard Digital Outputs

Relevant DMC Commands

DMC-1700/1800 Appendices

Coordinated Motion Mathematical Analysis

360

Velocity

DMC-1700/DMC-1000 Comparison

List of Other Publications

Training Seminars

Motion Control Made Easy

Warranty

Contacting Us

Index

DMC-1700/1800 Index

Flags

ICM-1100 25, 47, 48 Independent Motion

Quit

Stop