Technical Reference Guide

5.9.4 NIC PROGRAMMING

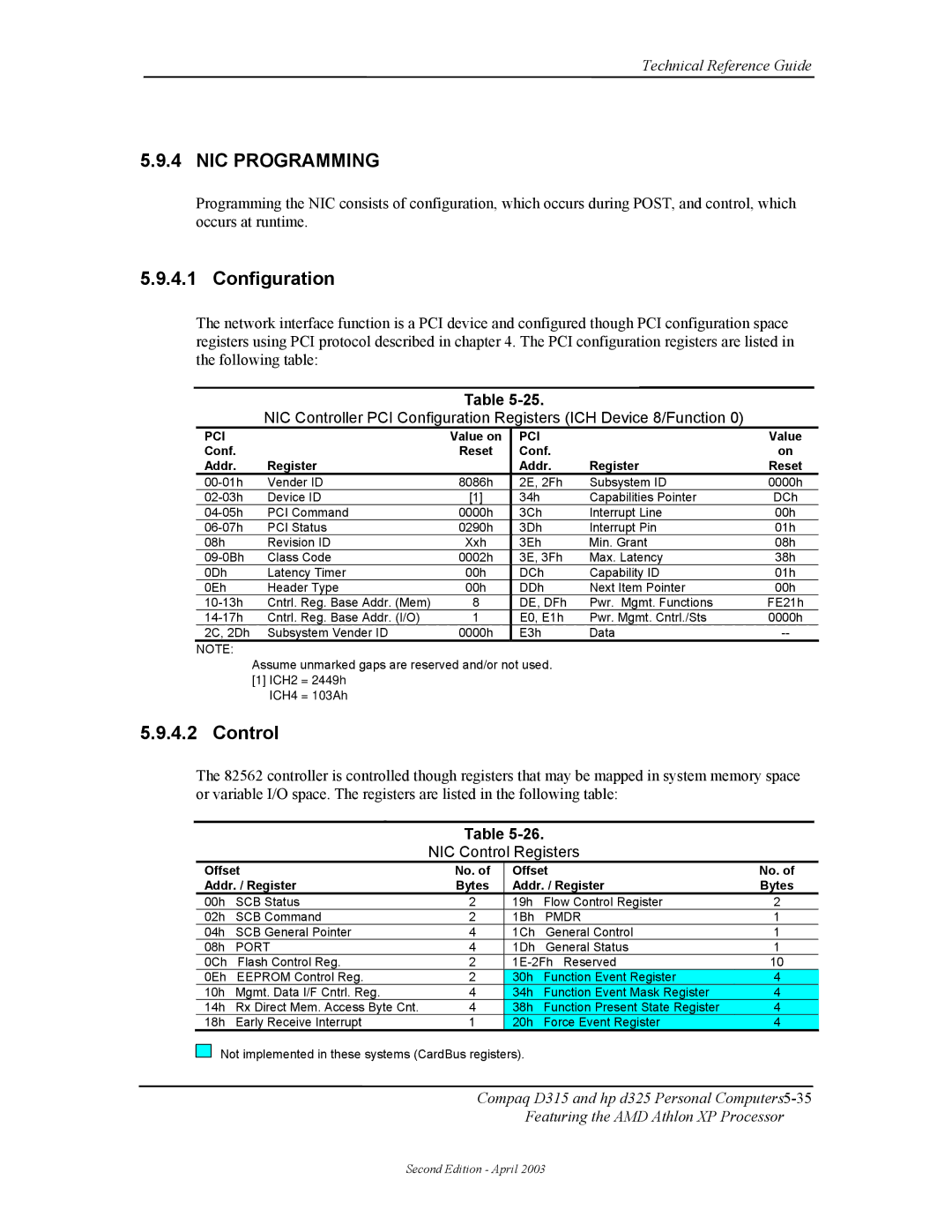

Programming the NIC consists of configuration, which occurs during POST, and control, which occurs at runtime.

5.9.4.1 Configuration

The network interface function is a PCI device and configured though PCI configuration space registers using PCI protocol described in chapter 4. The PCI configuration registers are listed in the following table:

Table

NIC Controller PCI Configuration Registers (ICH Device 8/Function 0)

PCI |

| Value on | PCI |

| Value |

Conf. |

| Reset | Conf. |

| on |

Addr. | Register |

| Addr. | Register | Reset |

Vender ID | 8086h | 2E, 2Fh | Subsystem ID | 0000h | |

Device ID | [1] | 34h | Capabilities Pointer | DCh | |

PCI Command | 0000h | 3Ch | Interrupt Line | 00h | |

PCI Status | 0290h | 3Dh | Interrupt Pin | 01h | |

08h | Revision ID | Xxh | 3Eh | Min. Grant | 08h |

Class Code | 0002h | 3E, 3Fh | Max. Latency | 38h | |

0Dh | Latency Timer | 00h | DCh | Capability ID | 01h |

0Eh | Header Type | 00h | DDh | Next Item Pointer | 00h |

Cntrl. Reg. Base Addr. (Mem) | 8 | DE, DFh | Pwr. Mgmt. Functions | FE21h | |

Cntrl. Reg. Base Addr. (I/O) | 1 | E0, E1h | Pwr. Mgmt. Cntrl./Sts | 0000h | |

2C, 2Dh | Subsystem Vender ID | 0000h | E3h | Data |

NOTE:

Assume unmarked gaps are reserved and/or not used.

[1]ICH2 = 2449h ICH4 = 103Ah

5.9.4.2Control

The 82562 controller is controlled though registers that may be mapped in system memory space or variable I/O space. The registers are listed in the following table:

Table

NIC Control Registers

Offset | No. of | Offset | No. of | ||

Addr. / Register | Bytes | Addr. / Register | Bytes | ||

00h | SCB Status | 2 | 19h | Flow Control Register | 2 |

02h | SCB Command | 2 | 1Bh | PMDR | 1 |

04h | SCB General Pointer | 4 | 1Ch | General Control | 1 |

08h | PORT | 4 | 1Dh | General Status | 1 |

0Ch | Flash Control Reg. | 2 | 10 | ||

0Eh | EEPROM Control Reg. | 2 | 30h | Function Event Register | 4 |

10h | Mgmt. Data I/F Cntrl. Reg. | 4 | 34h | Function Event Mask Register | 4 |

14h | Rx Direct Mem. Access Byte Cnt. | 4 | 38h | Function Present State Register | 4 |

18h | Early Receive Interrupt | 1 | 20h | Force Event Register | 4 |

Not implemented in these systems (CardBus registers).

Compaq D315 and hp d325 Personal

Featuring the AMD Athlon XP Processor

Second Edition - April 2003