Chapter 4 System Support

4.4SYSTEM RESOURCES

This section describes the availability and basic control of major subsystems, otherwise known as resource allocation or simply “system resources.” System resources are provided on a priority basis through hardware interrupts and DMA requests and grants.

4.4.1 INTERRUPTS

The microprocessor uses two types of hardware interrupts; maskable and nonmaskable. A maskable interrupt can be enabled or disabled within the microprocessor by the use of the STI and CLI instructions. A nonmaskable interrupt cannot be masked off within the microprocessor, although it may be inhibited by hardware or software means external to the microprocessor.

4.4.1.1Maskable Interrupts

The maskable interrupt is a

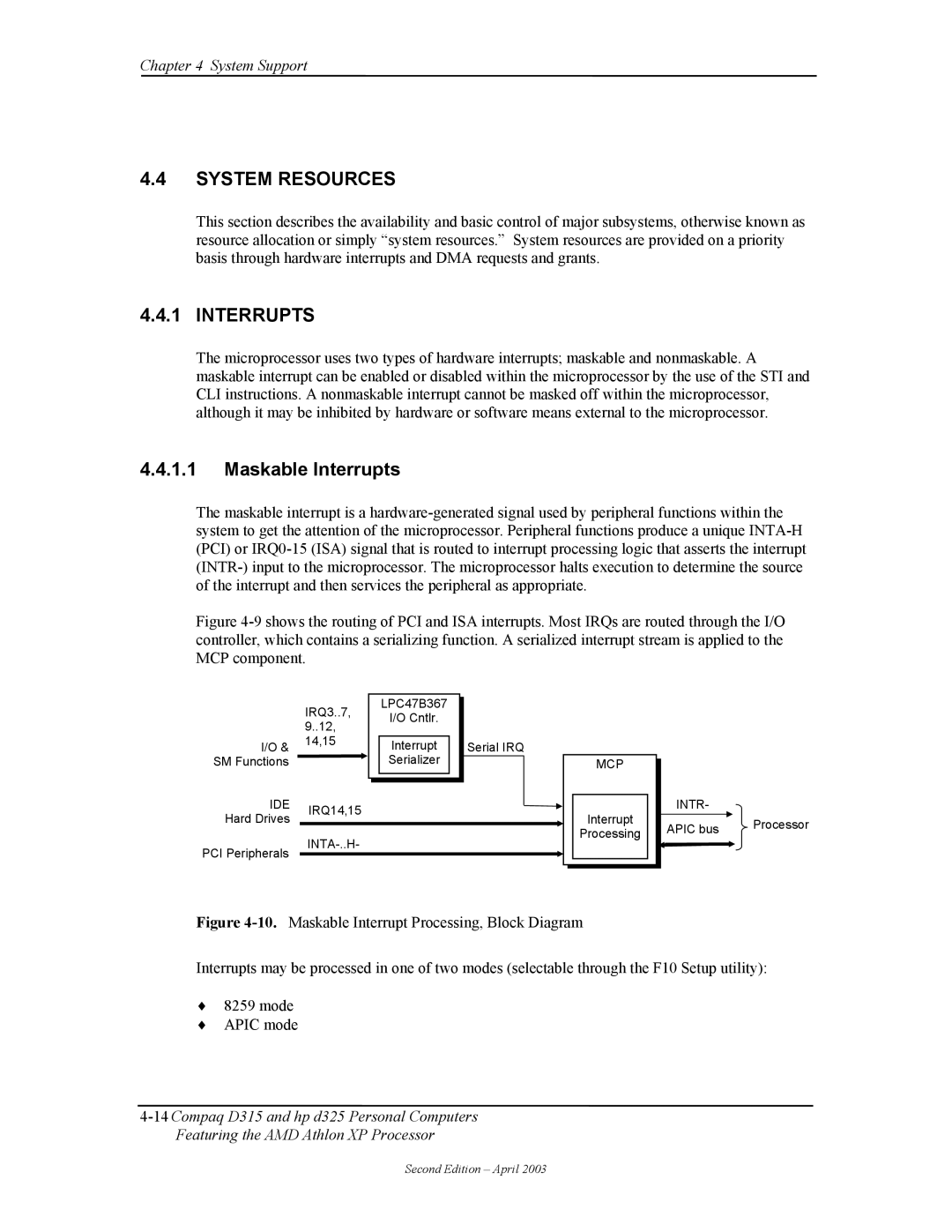

Figure 4-9 shows the routing of PCI and ISA interrupts. Most IRQs are routed through the I/O controller, which contains a serializing function. A serialized interrupt stream is applied to the MCP component.

I/O & SM Functions

IRQ3..7, 9..12, 14,15

LPC47B367

I/O Cntlr.

Interrupt

Serializer

Serial IRQ

MCP

IDE IRQ14,15 Hard Drives

Interrupt

INTR-

Processor |

PCI Peripherals

INTA-..H-

Processing

APIC bus |

Figure 4-10. Maskable Interrupt Processing, Block Diagram

Interrupts may be processed in one of two modes (selectable through the F10 Setup utility):

♦8259 mode

♦APIC mode

Second Edition – April 2003