Chapter 5 Input/Output Interfaces

5.6KEYBOARD/POINTING DEVICE INTERFACE

The keyboard/pointing device interface function is provided by the LPC47B367 I/O controller component, which integrates

5.6.1KEYBOARD INTERFACE OPERATION

The data/clock link between the 8042 and the keyboard is

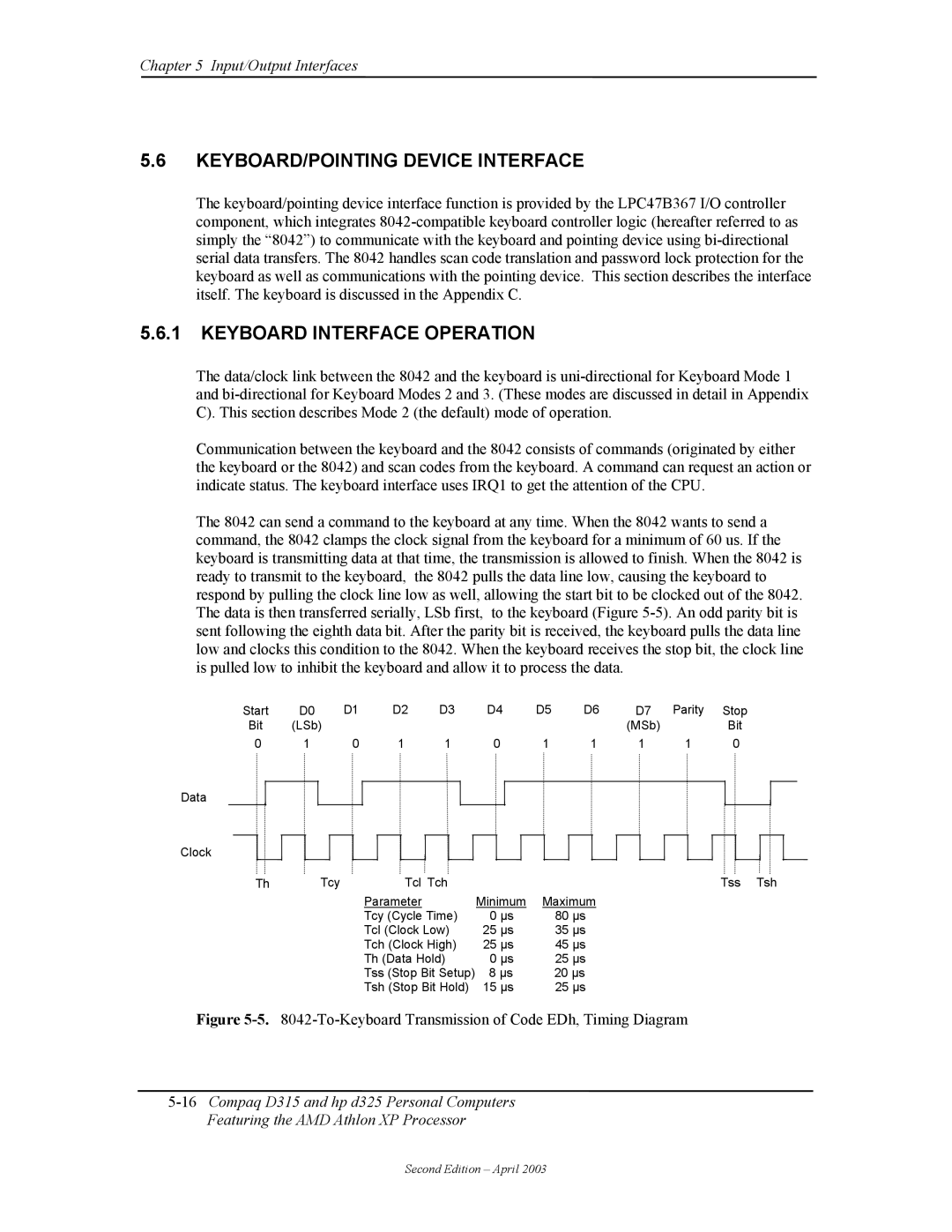

Communication between the keyboard and the 8042 consists of commands (originated by either the keyboard or the 8042) and scan codes from the keyboard. A command can request an action or indicate status. The keyboard interface uses IRQ1 to get the attention of the CPU.

The 8042 can send a command to the keyboard at any time. When the 8042 wants to send a command, the 8042 clamps the clock signal from the keyboard for a minimum of 60 us. If the keyboard is transmitting data at that time, the transmission is allowed to finish. When the 8042 is ready to transmit to the keyboard, the 8042 pulls the data line low, causing the keyboard to respond by pulling the clock line low as well, allowing the start bit to be clocked out of the 8042. The data is then transferred serially, LSb first, to the keyboard (Figure

Start | D0 | D1 | D2 | D3 | D4 | D5 | D6 | D7 | Parity | Stop |

Bit | (LSb) |

|

|

|

|

|

| (MSb) |

| Bit |

0 | 1 | 0 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 0 |

Data

Clock

Th | Tcy | Tcl Tch |

|

| Tss Tsh |

|

| Parameter | Minimum | Maximum | |

|

| Tcy (Cycle Time) | 0 | µs | 80 µs |

|

| Tcl (Clock Low) | 25 | µs | 35 µs |

|

| Tch (Clock High) | 25 | µs | 45 µs |

|

| Th (Data Hold) | 0 | µs | 25 µs |

|

| Tss (Stop Bit Setup) | 8 µs | 20 µs | |

|

| Tsh (Stop Bit Hold) | 15 | µs | 25 µs |

Figure 5-5. 8042-To-Keyboard Transmission of Code EDh, Timing Diagram

Second Edition – April 2003