Chapter 4 System Support

The PCI interrupts can be configured by PCI Configuration Registers 60h..63h to share the standard ISA interrupts (IRQn).

NOTE: The APIC mode is supported by the Windows NT, Windows 2000, and Windows XP operating systems. Systems running the Windows 95 or 98 operating system will need to run in 8259 mode.

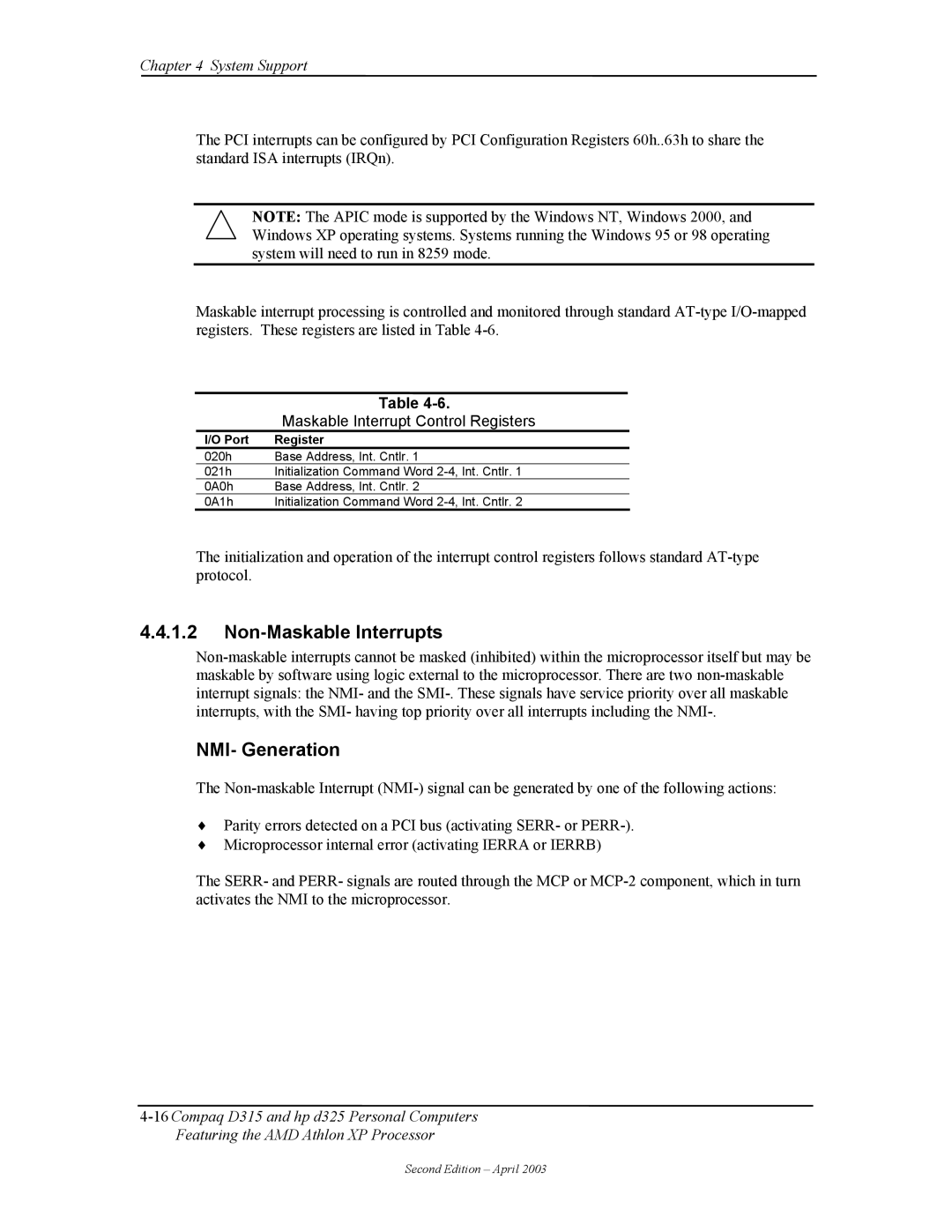

Maskable interrupt processing is controlled and monitored through standard

Table

| Table |

| Maskable Interrupt Control Registers |

I/O Port | Register |

020h | Base Address, Int. Cntlr. 1 |

021h | Initialization Command Word |

0A0h | Base Address, Int. Cntlr. 2 |

0A1h | Initialization Command Word |

The initialization and operation of the interrupt control registers follows standard

4.4.1.2Non-Maskable Interrupts

NMI- Generation

The

♦Parity errors detected on a PCI bus (activating SERR- or

♦Microprocessor internal error (activating IERRA or IERRB)

The SERR- and PERR- signals are routed through the MCP or

Second Edition – April 2003