Chapter 4 System Support

DMA controller 1 can move up to 64 Kbytes of data per DMA transfer. DMA controller 2 can move up to 64 Kwords (128 Kbytes) of data per DMA transfer. Word DMA operations are only possible between

The RAM refresh is designed to perform a memory read cycle on each of the 512 row addresses in the DRAM memory space. Refresh operations are used to refresh memory on the

The remaining address lines are in an undefined state during the refresh cycle. The refresh operations are driven by a

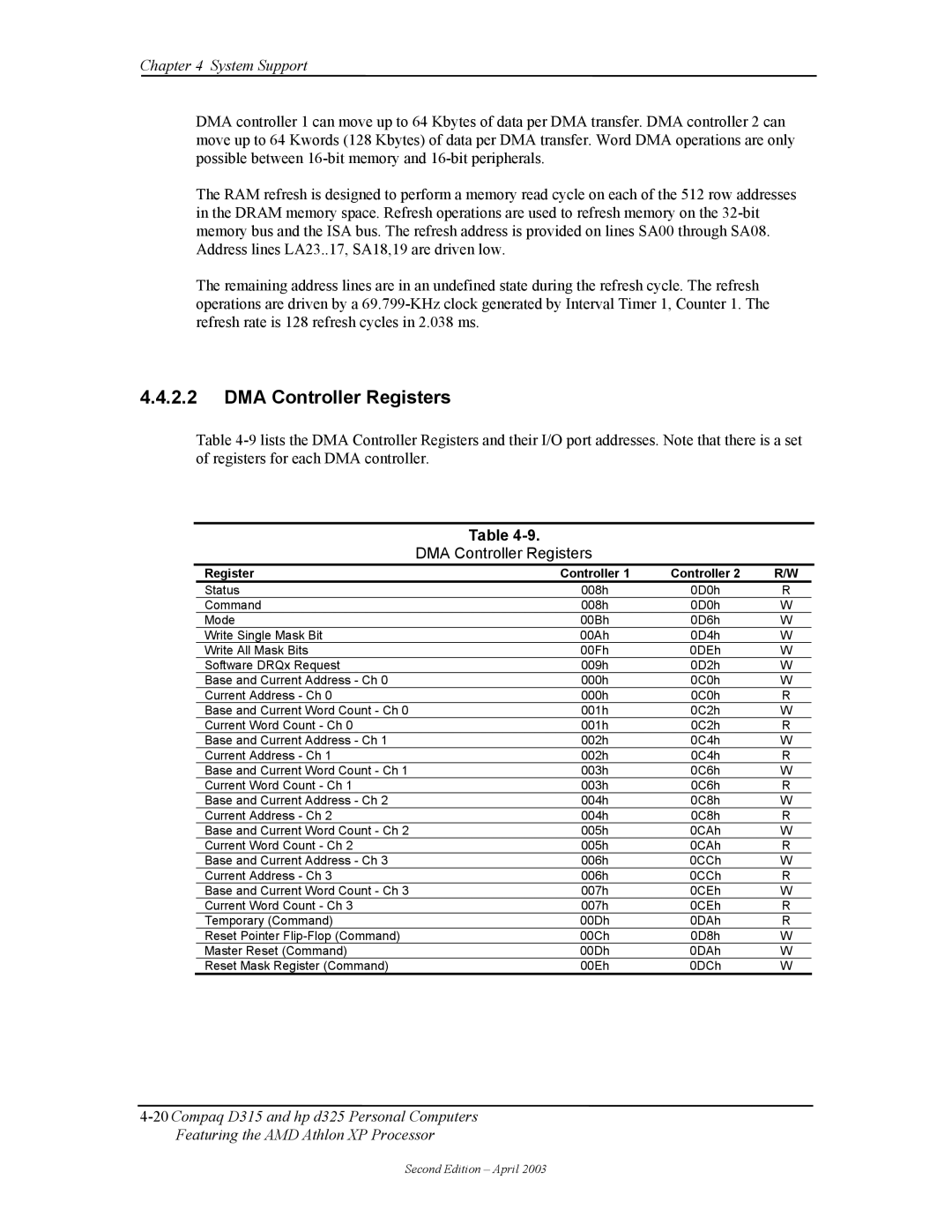

4.4.2.2DMA Controller Registers

Table

Table

Table

DMA Controller Registers

| Register | Controller 1 | Controller 2 | R/W | |

| Status | 008h | 0D0h | R |

|

| Command | 008h | 0D0h | W |

|

| Mode | 00Bh | 0D6h | W |

|

| Write Single Mask Bit | 00Ah | 0D4h | W |

|

| Write All Mask Bits | 00Fh | 0DEh | W |

|

| Software DRQx Request | 009h | 0D2h | W |

|

| Base and Current Address - Ch 0 | 000h | 0C0h | W |

|

| Current Address - Ch 0 | 000h | 0C0h | R |

|

| Base and Current Word Count - Ch 0 | 001h | 0C2h | W |

|

| Current Word Count - Ch 0 | 001h | 0C2h | R |

|

| Base and Current Address - Ch 1 | 002h | 0C4h | W |

|

| Current Address - Ch 1 | 002h | 0C4h | R |

|

| Base and Current Word Count - Ch 1 | 003h | 0C6h | W |

|

| Current Word Count - Ch 1 | 003h | 0C6h | R |

|

| Base and Current Address - Ch 2 | 004h | 0C8h | W |

|

| Current Address - Ch 2 | 004h | 0C8h | R |

|

| Base and Current Word Count - Ch 2 | 005h | 0CAh | W |

|

| Current Word Count - Ch 2 | 005h | 0CAh | R |

|

| Base and Current Address - Ch 3 | 006h | 0CCh | W |

|

| Current Address - Ch 3 | 006h | 0CCh | R |

|

| Base and Current Word Count - Ch 3 | 007h | 0CEh | W |

|

| Current Word Count - Ch 3 | 007h | 0CEh | R |

|

| Temporary (Command) | 00Dh | 0DAh | R |

|

| Reset Pointer | 00Ch | 0D8h | W |

|

| Master Reset (Command) | 00Dh | 0DAh | W |

|

| Reset Mask Register (Command) | 00Eh | 0DCh | W |

|

Second Edition – April 2003