Appendix D Compaq/Intel Network Interface Controller Adapters

D.4 ADAPTER PROGRAMMING

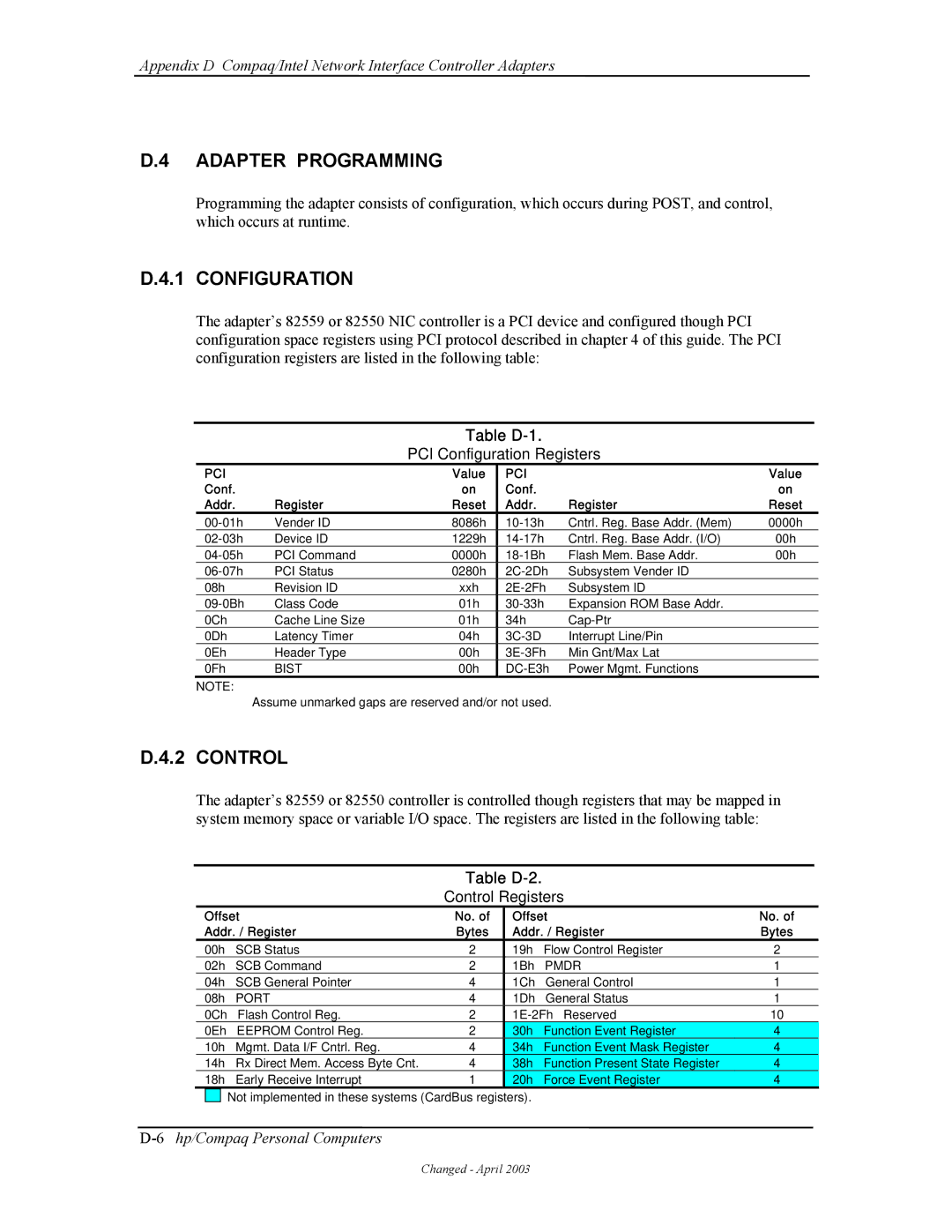

Programming the adapter consists of configuration, which occurs during POST, and control, which occurs at runtime.

D.4.1 CONFIGURATION

The adapter’s 82559 or 82550 NIC controller is a PCI device and configured though PCI configuration space registers using PCI protocol described in chapter 4 of this guide. The PCI configuration registers are listed in the following table:

Table

Table D-1.

PCI Configuration Registers

PCI |

| Value | PCI |

| Value |

Conf. |

| on | Conf. |

| on |

Addr. | Register | Reset | Addr. | Register | Reset |

Vender ID | 8086h | Cntrl. Reg. Base Addr. (Mem) | 0000h | ||

Device ID | 1229h | Cntrl. Reg. Base Addr. (I/O) | 00h | ||

PCI Command | 0000h | Flash Mem. Base Addr. | 00h | ||

PCI Status | 0280h | Subsystem Vender ID |

| ||

08h | Revision ID | xxh | Subsystem ID |

| |

Class Code | 01h | Expansion ROM Base Addr. |

| ||

0Ch | Cache Line Size | 01h | 34h |

| |

0Dh | Latency Timer | 04h | Interrupt Line/Pin |

| |

0Eh | Header Type | 00h | Min Gnt/Max Lat |

| |

0Fh | BIST | 00h | Power Mgmt. Functions |

|

NOTE:

Assume unmarked gaps are reserved and/or not used.

D.4.2 CONTROL

The adapter’s 82559 or 82550 controller is controlled though registers that may be mapped in system memory space or variable I/O space. The registers are listed in the following table:

Table

Table D-2.

Control Registers

Offset | No. of | Offset | No. of | ||||

Addr. / Register | Bytes | Addr. / Register | Bytes | ||||

00h | SCB Status | 2 | 19h | Flow Control Register | 2 | ||

02h | SCB Command | 2 | 1Bh | PMDR | 1 | ||

04h | SCB General Pointer | 4 | 1Ch | General Control | 1 | ||

08h | PORT | 4 | 1Dh | General Status | 1 | ||

0Ch | Flash Control Reg. | 2 | 10 | ||||

0Eh | EEPROM Control Reg. | 2 | 30h | Function Event Register | 4 | ||

10h | Mgmt. Data I/F Cntrl. Reg. | 4 | 34h | Function Event Mask Register | 4 | ||

14h | Rx Direct Mem. Access Byte Cnt. | 4 | 38h | Function Present State Register | 4 | ||

18h | Early Receive Interrupt | 1 | 20h | Force Event Register | 4 | ||

|

|

| Not implemented in these systems (CardBus registers). |

|

| ||

Changed - April 2003