Chapter 4 System Support

4.8REGISTER MAP AND MISCELLANEOUS FUNCTIONS

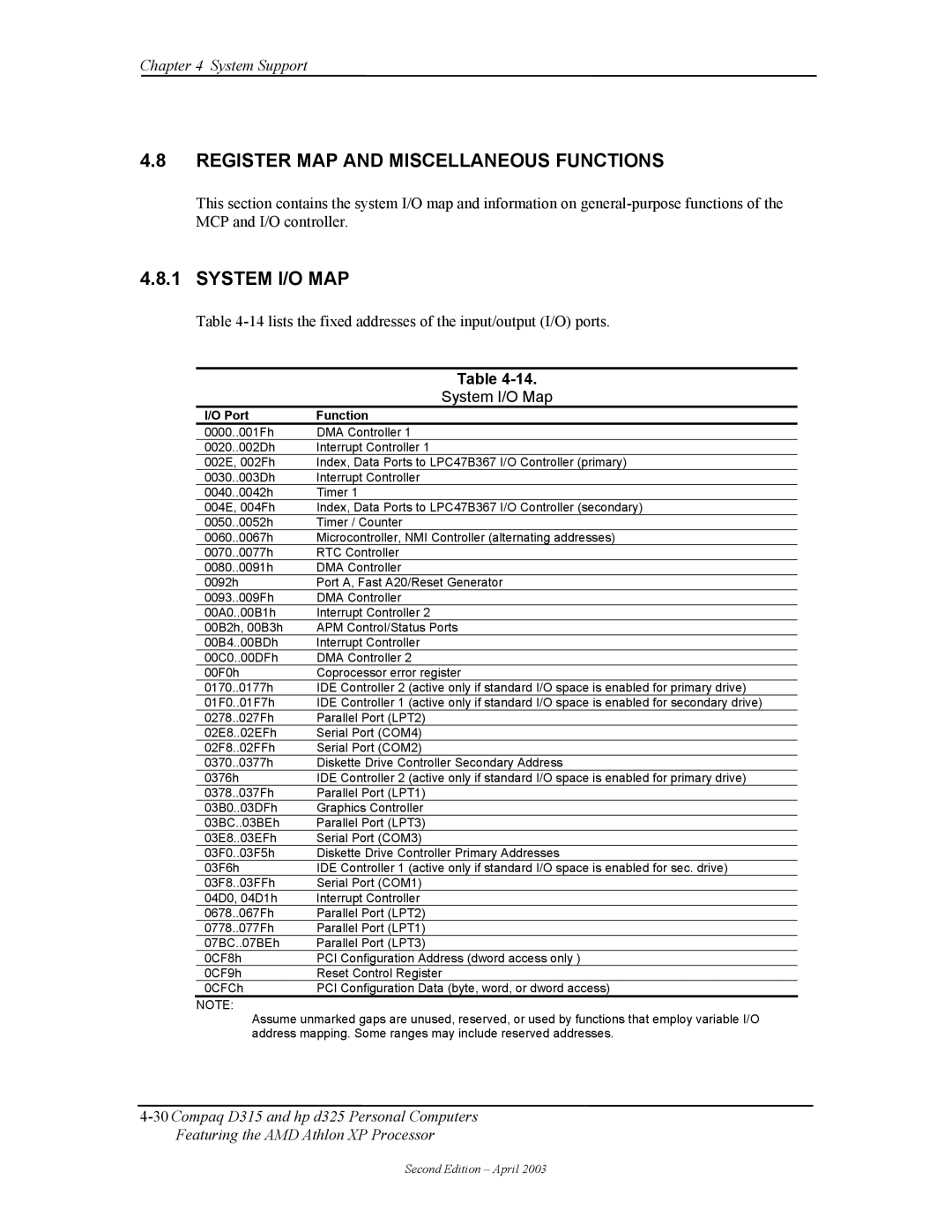

This section contains the system I/O map and information on

4.8.1 SYSTEM I/O MAP

Table

Table

| Table |

| System I/O Map |

I/O Port | Function |

0000..001Fh | DMA Controller 1 |

0020..002Dh | Interrupt Controller 1 |

002E, 002Fh | Index, Data Ports to LPC47B367 I/O Controller (primary) |

0030..003Dh | Interrupt Controller |

0040..0042h | Timer 1 |

004E, 004Fh | Index, Data Ports to LPC47B367 I/O Controller (secondary) |

0050..0052h | Timer / Counter |

0060..0067h | Microcontroller, NMI Controller (alternating addresses) |

0070..0077h | RTC Controller |

0080..0091h | DMA Controller |

0092h | Port A, Fast A20/Reset Generator |

0093..009Fh | DMA Controller |

00A0..00B1h | Interrupt Controller 2 |

00B2h, 00B3h | APM Control/Status Ports |

00B4..00BDh | Interrupt Controller |

00C0..00DFh | DMA Controller 2 |

00F0h | Coprocessor error register |

0170..0177h | IDE Controller 2 (active only if standard I/O space is enabled for primary drive) |

01F0..01F7h | IDE Controller 1 (active only if standard I/O space is enabled for secondary drive) |

0278..027Fh | Parallel Port (LPT2) |

02E8..02EFh | Serial Port (COM4) |

02F8..02FFh | Serial Port (COM2) |

0370..0377h | Diskette Drive Controller Secondary Address |

0376h | IDE Controller 2 (active only if standard I/O space is enabled for primary drive) |

0378..037Fh | Parallel Port (LPT1) |

03B0..03DFh | Graphics Controller |

03BC..03BEh | Parallel Port (LPT3) |

03E8..03EFh | Serial Port (COM3) |

03F0..03F5h | Diskette Drive Controller Primary Addresses |

03F6h | IDE Controller 1 (active only if standard I/O space is enabled for sec. drive) |

03F8..03FFh | Serial Port (COM1) |

04D0, 04D1h | Interrupt Controller |

0678..067Fh | Parallel Port (LPT2) |

0778..077Fh | Parallel Port (LPT1) |

07BC..07BEh | Parallel Port (LPT3) |

0CF8h | PCI Configuration Address (dword access only ) |

0CF9h | Reset Control Register |

0CFCh | PCI Configuration Data (byte, word, or dword access) |

NOTE:

Assume unmarked gaps are unused, reserved, or used by functions that employ variable I/O address mapping. Some ranges may include reserved addresses.

Second Edition – April 2003