Technical Reference Guide

4.2.1 PCI BUS TRANSACTIONS

The PCI bus consists of a

4.2.1.1I/O and Memory Cycles

For I/O and memory cycles, a standard

4.2.1.2Configuration Cycles

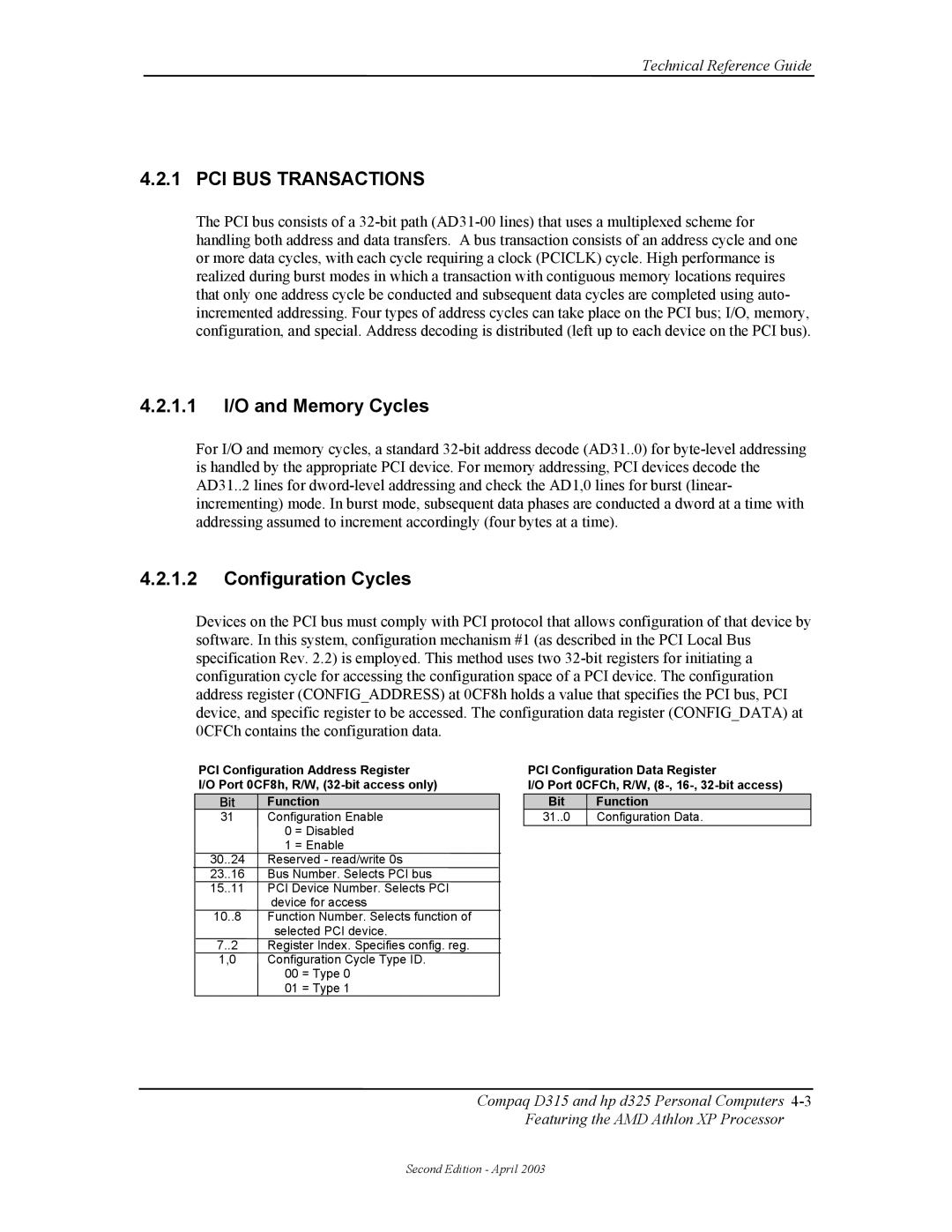

Devices on the PCI bus must comply with PCI protocol that allows configuration of that device by software. In this system, configuration mechanism #1 (as described in the PCI Local Bus specification Rev. 2.2) is employed. This method uses two

PCI Configuration Address Register

I/O Port 0CF8h, R/W,

Bit | Function |

31 | Configuration Enable |

| 0 = Disabled |

| 1 = Enable |

30..24 | Reserved - read/write 0s |

23..16 | Bus Number. Selects PCI bus |

15..11 | PCI Device Number. Selects PCI |

| device for access |

10..8 | Function Number. Selects function of |

| selected PCI device. |

7..2 | Register Index. Specifies config. reg. |

1,0 | Configuration Cycle Type ID. |

| 00 = Type 0 |

| 01 = Type 1 |

PCI Configuration Data Register

I/O Port 0CFCh, R/W,

Bit Function

31..0 Configuration Data.

Compaq D315 and hp d325 Personal Computers

Second Edition - April 2003