|

| PM5349 |

| |

|

|

| ||

|

|

|

| |

DATASHEET |

|

|

|

|

|

|

|

| |

|

|

|

| |

ISSUE 6 |

| SATURN USER NETWORK INTERFACE |

| |

|

|

|

|

|

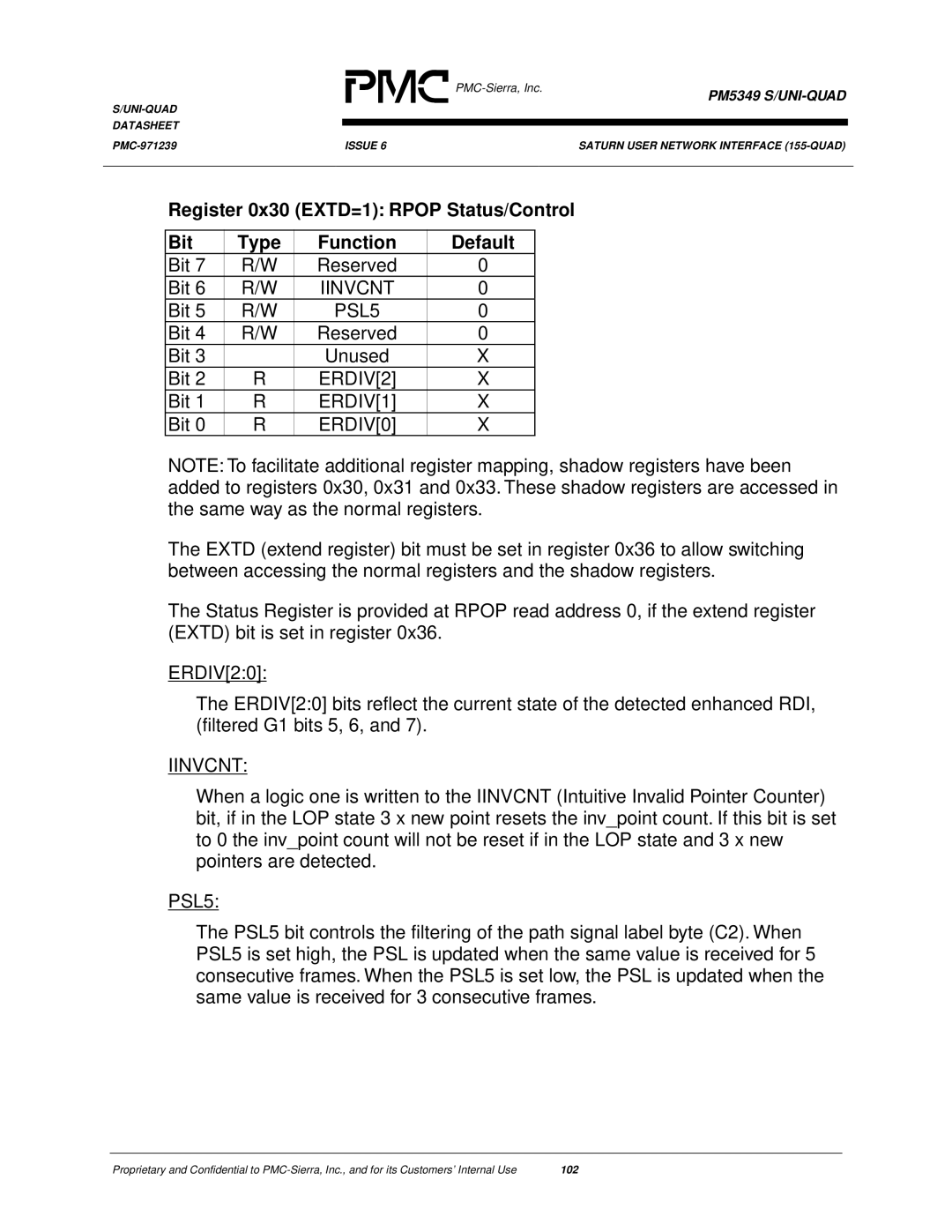

Register 0x30 (EXTD=1): RPOP Status/Control

Bit | Type | Function | Default |

Bit 7 | R/W | Reserved | 0 |

Bit 6 | R/W | IINVCNT | 0 |

Bit 5 | R/W | PSL5 | 0 |

Bit 4 | R/W | Reserved | 0 |

Bit 3 |

| Unused | X |

Bit 2 | R | ERDIV[2] | X |

Bit 1 | R | ERDIV[1] | X |

Bit 0 | R | ERDIV[0] | X |

NOTE: To facilitate additional register mapping, shadow registers have been added to registers 0x30, 0x31 and 0x33. These shadow registers are accessed in the same way as the normal registers.

The EXTD (extend register) bit must be set in register 0x36 to allow switching between accessing the normal registers and the shadow registers.

The Status Register is provided at RPOP read address 0, if the extend register (EXTD) bit is set in register 0x36.

ERDIV[2:0]:

The ERDIV[2:0] bits reflect the current state of the detected enhanced RDI, (filtered G1 bits 5, 6, and 7).

IINVCNT:

When a logic one is written to the IINVCNT (Intuitive Invalid Pointer Counter) bit, if in the LOP state 3 x new point resets the inv_point count. If this bit is set to 0 the inv_point count will not be reset if in the LOP state and 3 x new pointers are detected.

PSL5:

The PSL5 bit controls the filtering of the path signal label byte (C2). When PSL5 is set high, the PSL is updated when the same value is received for 5 consecutive frames. When the PSL5 is set low, the PSL is updated when the same value is received for 3 consecutive frames.

Proprietary and Confidential to | 102 |