|

| PM5349 |

| |

|

|

| ||

|

|

|

| |

DATASHEET |

|

|

|

|

|

|

|

| |

|

|

|

| |

ISSUE 6 |

| SATURN USER NETWORK INTERFACE |

| |

|

|

|

|

|

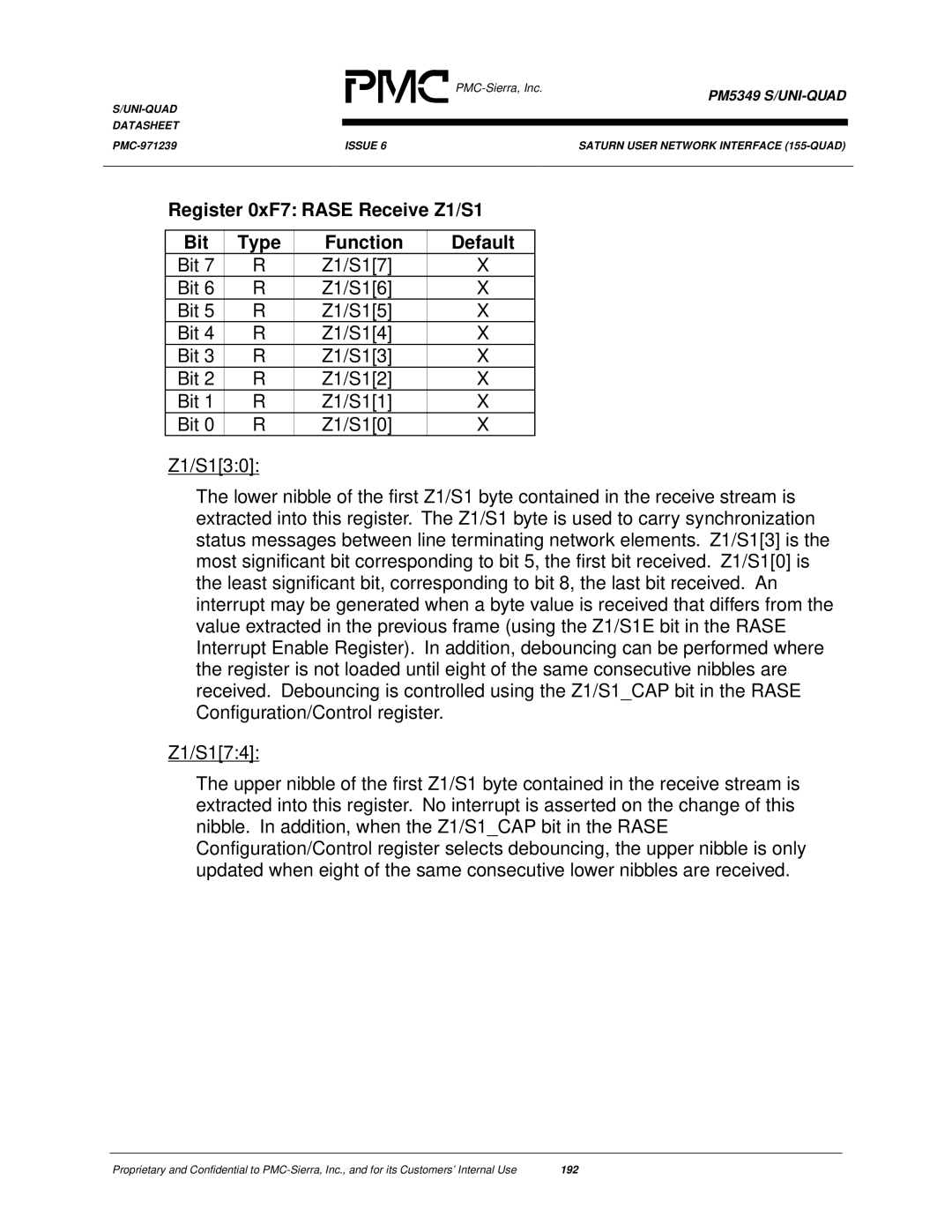

Register 0xF7: RASE Receive Z1/S1

Bit | Type | Function | Default |

Bit 7 | R | Z1/S1[7] | X |

Bit 6 | R | Z1/S1[6] | X |

Bit 5 | R | Z1/S1[5] | X |

Bit 4 | R | Z1/S1[4] | X |

Bit 3 | R | Z1/S1[3] | X |

Bit 2 | R | Z1/S1[2] | X |

Bit 1 | R | Z1/S1[1] | X |

Bit 0 | R | Z1/S1[0] | X |

Z1/S1[3:0]:

The lower nibble of the first Z1/S1 byte contained in the receive stream is extracted into this register. The Z1/S1 byte is used to carry synchronization status messages between line terminating network elements. Z1/S1[3] is the most significant bit corresponding to bit 5, the first bit received. Z1/S1[0] is the least significant bit, corresponding to bit 8, the last bit received. An interrupt may be generated when a byte value is received that differs from the value extracted in the previous frame (using the Z1/S1E bit in the RASE Interrupt Enable Register). In addition, debouncing can be performed where the register is not loaded until eight of the same consecutive nibbles are received. Debouncing is controlled using the Z1/S1_CAP bit in the RASE Configuration/Control register.

Z1/S1[7:4]:

The upper nibble of the first Z1/S1 byte contained in the receive stream is extracted into this register. No interrupt is asserted on the change of this nibble. In addition, when the Z1/S1_CAP bit in the RASE Configuration/Control register selects debouncing, the upper nibble is only updated when eight of the same consecutive lower nibbles are received.

Proprietary and Confidential to | 192 |