DATASHEET

PM5349 S/UNI-QUAD

ISSUE 6 | SATURN USER NETWORK INTERFACE | |

|

|

|

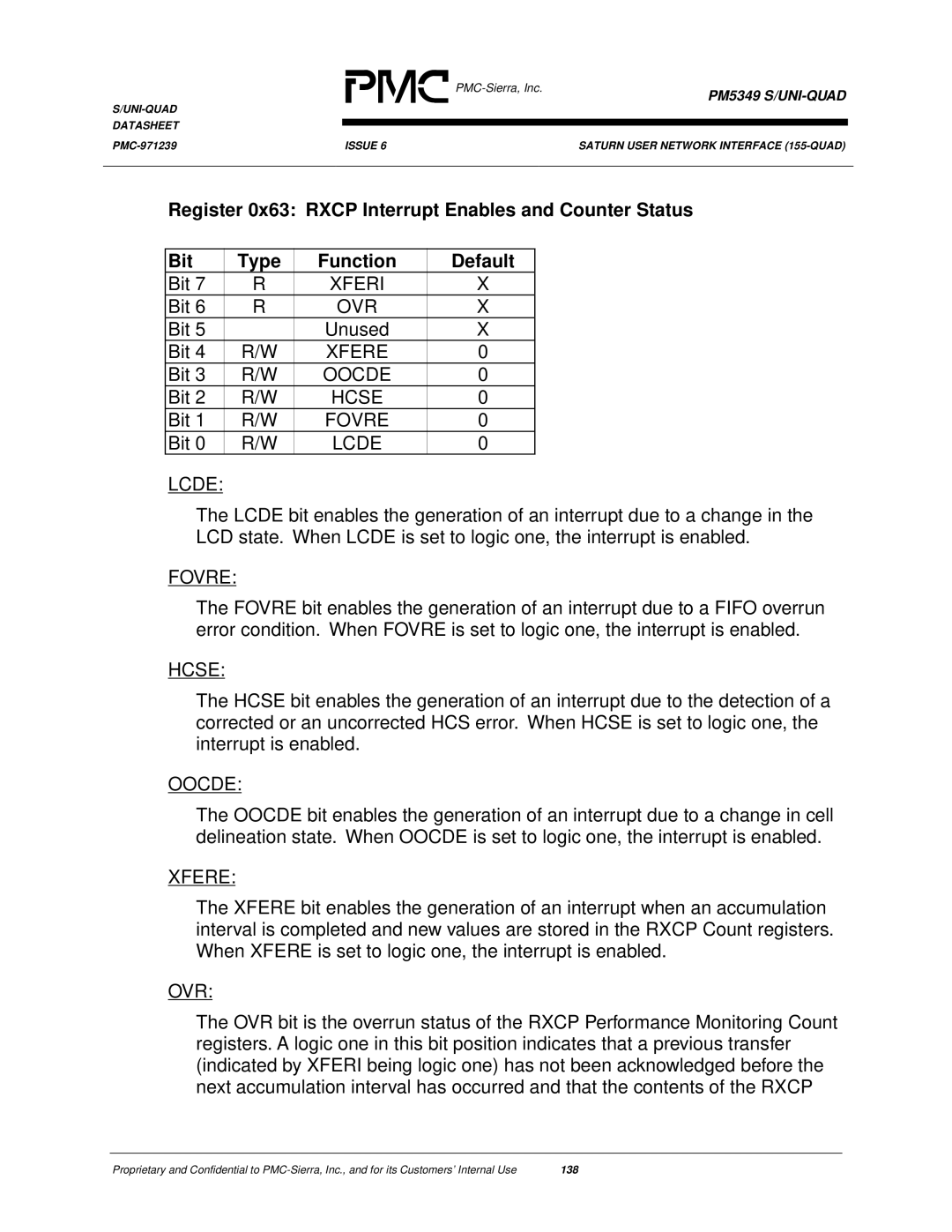

Register 0x63: RXCP Interrupt Enables and Counter Status

Bit | Type | Function | Default |

Bit 7 | R | XFERI | X |

Bit 6 | R | OVR | X |

Bit 5 |

| Unused | X |

Bit 4 | R/W | XFERE | 0 |

Bit 3 | R/W | OOCDE | 0 |

Bit 2 | R/W | HCSE | 0 |

Bit 1 | R/W | FOVRE | 0 |

Bit 0 | R/W | LCDE | 0 |

LCDE:

The LCDE bit enables the generation of an interrupt due to a change in the LCD state. When LCDE is set to logic one, the interrupt is enabled.

FOVRE:

The FOVRE bit enables the generation of an interrupt due to a FIFO overrun error condition. When FOVRE is set to logic one, the interrupt is enabled.

HCSE:

The HCSE bit enables the generation of an interrupt due to the detection of a corrected or an uncorrected HCS error. When HCSE is set to logic one, the interrupt is enabled.

OOCDE:

The OOCDE bit enables the generation of an interrupt due to a change in cell delineation state. When OOCDE is set to logic one, the interrupt is enabled.

XFERE:

The XFERE bit enables the generation of an interrupt when an accumulation interval is completed and new values are stored in the RXCP Count registers. When XFERE is set to logic one, the interrupt is enabled.

OVR:

The OVR bit is the overrun status of the RXCP Performance Monitoring Count registers. A logic one in this bit position indicates that a previous transfer (indicated by XFERI being logic one) has not been acknowledged before the next accumulation interval has occurred and that the contents of the RXCP

Proprietary and Confidential to | 138 |