DATASHEET

PM5349 S/UNI-QUAD

ISSUE 6 | SATURN USER NETWORK INTERFACE | |

|

|

|

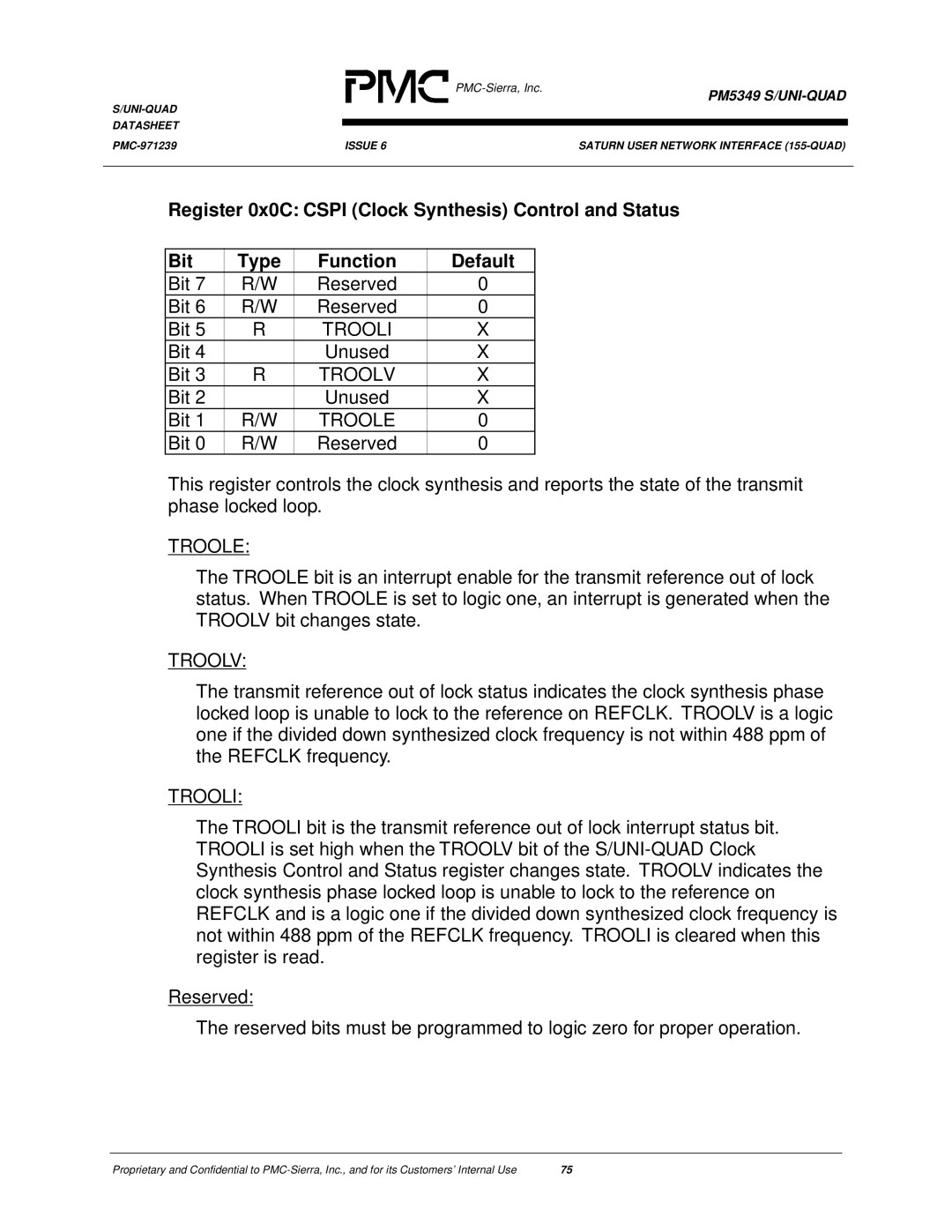

Register 0x0C: CSPI (Clock Synthesis) Control and Status

Bit | Type | Function | Default |

Bit 7 | R/W | Reserved | 0 |

Bit 6 | R/W | Reserved | 0 |

Bit 5 | R | TROOLI | X |

Bit 4 |

| Unused | X |

Bit 3 | R | TROOLV | X |

Bit 2 |

| Unused | X |

Bit 1 | R/W | TROOLE | 0 |

Bit 0 | R/W | Reserved | 0 |

This register controls the clock synthesis and reports the state of the transmit phase locked loop.

TROOLE:

The TROOLE bit is an interrupt enable for the transmit reference out of lock status. When TROOLE is set to logic one, an interrupt is generated when the TROOLV bit changes state.

TROOLV:

The transmit reference out of lock status indicates the clock synthesis phase locked loop is unable to lock to the reference on REFCLK. TROOLV is a logic one if the divided down synthesized clock frequency is not within 488 ppm of the REFCLK frequency.

TROOLI:

The TROOLI bit is the transmit reference out of lock interrupt status bit. TROOLI is set high when the TROOLV bit of the

Reserved:

The reserved bits must be programmed to logic zero for proper operation.

Proprietary and Confidential to | 75 |