DATASHEET

PM5349 S/UNI-QUAD

ISSUE 6 | SATURN USER NETWORK INTERFACE | |

|

|

|

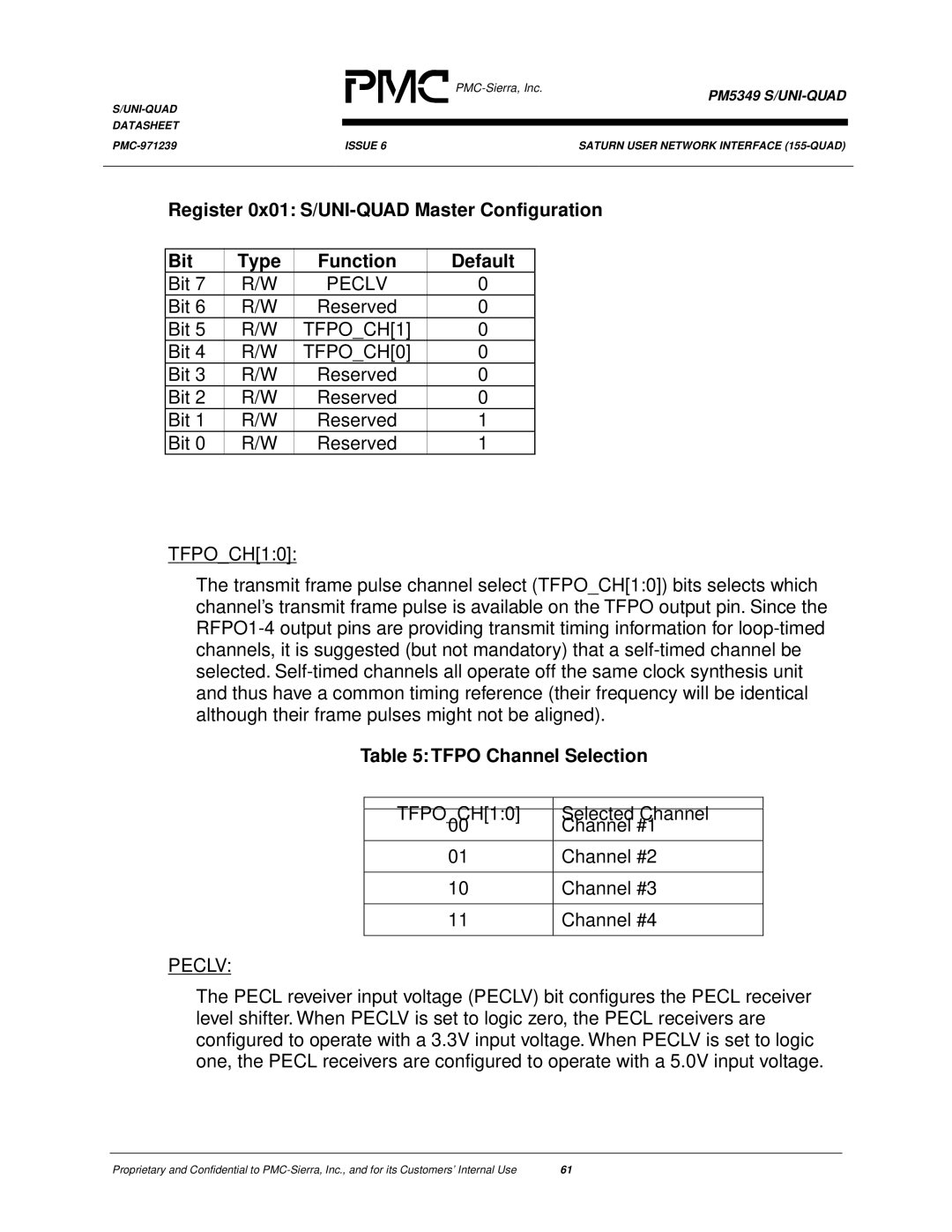

Register 0x01:

Bit | Type | Function | Default |

Bit 7 | R/W | PECLV | 0 |

Bit 6 | R/W | Reserved | 0 |

Bit 5 | R/W | TFPO_CH[1] | 0 |

Bit 4 | R/W | TFPO_CH[0] | 0 |

Bit 3 | R/W | Reserved | 0 |

Bit 2 | R/W | Reserved | 0 |

Bit 1 | R/W | Reserved | 1 |

Bit 0 | R/W | Reserved | 1 |

TFPO_CH[1:0]:

The transmit frame pulse channel select (TFPO_CH[1:0]) bits selects which channel’s transmit frame pulse is available on the TFPO output pin. Since the

Table 5: TFPO Channel Selection

TFPO_CH[1:0] | Selected Channel | |

00 | Channel #1 | |

01 | Channel #2 | |

|

| |

10 | Channel #3 | |

|

| |

11 | Channel #4 | |

|

|

PECLV:

The PECL reveiver input voltage (PECLV) bit configures the PECL receiver level shifter. When PECLV is set to logic zero, the PECL receivers are configured to operate with a 3.3V input voltage. When PECLV is set to logic one, the PECL receivers are configured to operate with a 5.0V input voltage.

Proprietary and Confidential to | 61 |