DATASHEET

PM5349 S/UNI-QUAD

ISSUE 6 | SATURN USER NETWORK INTERFACE | |

|

|

|

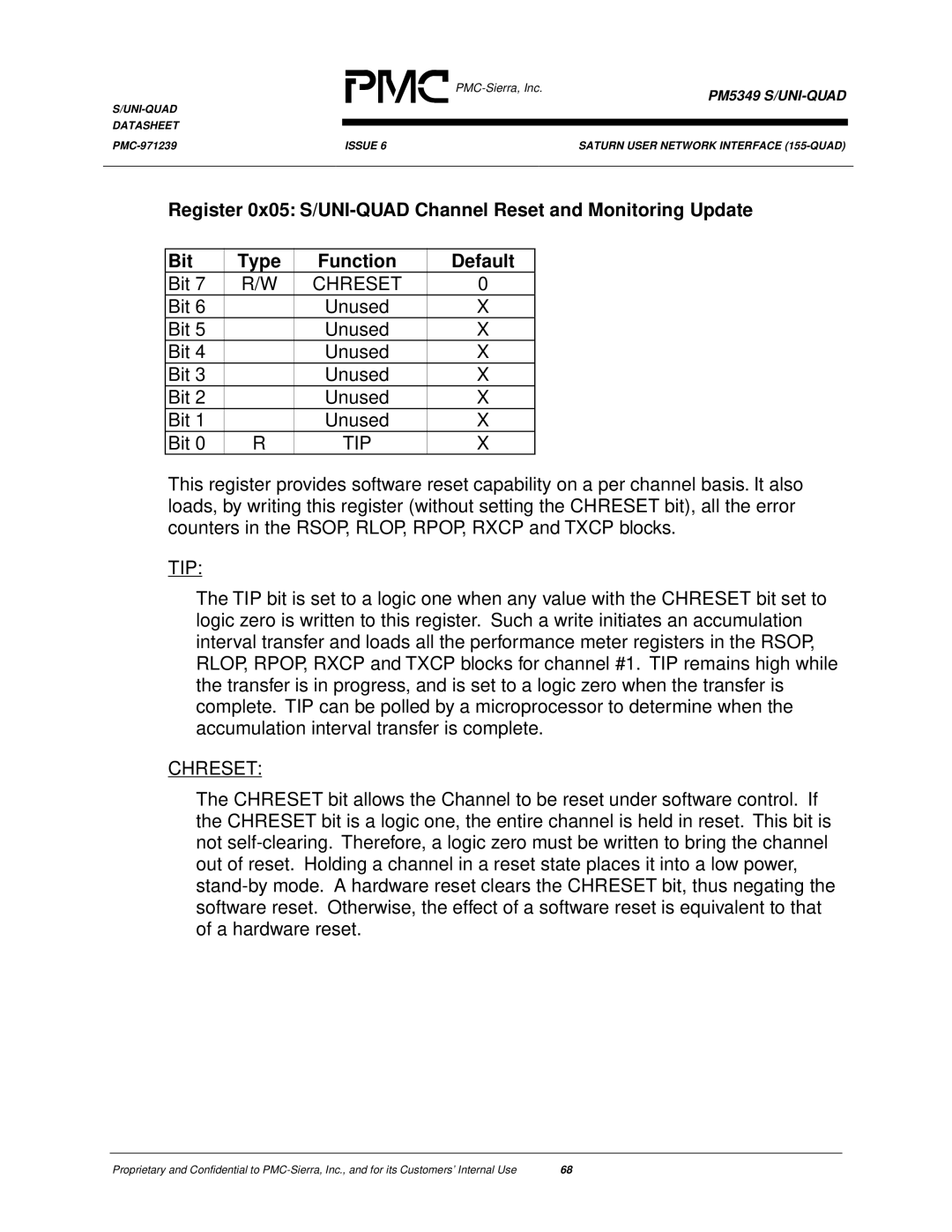

Register 0x05:

Bit | Type | Function | Default |

Bit 7 | R/W | CHRESET | 0 |

Bit 6 |

| Unused | X |

Bit 5 |

| Unused | X |

Bit 4 |

| Unused | X |

Bit 3 |

| Unused | X |

Bit 2 |

| Unused | X |

Bit 1 |

| Unused | X |

Bit 0 | R | TIP | X |

This register provides software reset capability on a per channel basis. It also loads, by writing this register (without setting the CHRESET bit), all the error counters in the RSOP, RLOP, RPOP, RXCP and TXCP blocks.

TIP:

The TIP bit is set to a logic one when any value with the CHRESET bit set to logic zero is written to this register. Such a write initiates an accumulation interval transfer and loads all the performance meter registers in the RSOP, RLOP, RPOP, RXCP and TXCP blocks for channel #1. TIP remains high while the transfer is in progress, and is set to a logic zero when the transfer is complete. TIP can be polled by a microprocessor to determine when the accumulation interval transfer is complete.

CHRESET:

The CHRESET bit allows the Channel to be reset under software control. If the CHRESET bit is a logic one, the entire channel is held in reset. This bit is not

Proprietary and Confidential to | 68 |