DATASHEET

PM5349 S/UNI-QUAD

ISSUE 6 | SATURN USER NETWORK INTERFACE | |

|

|

|

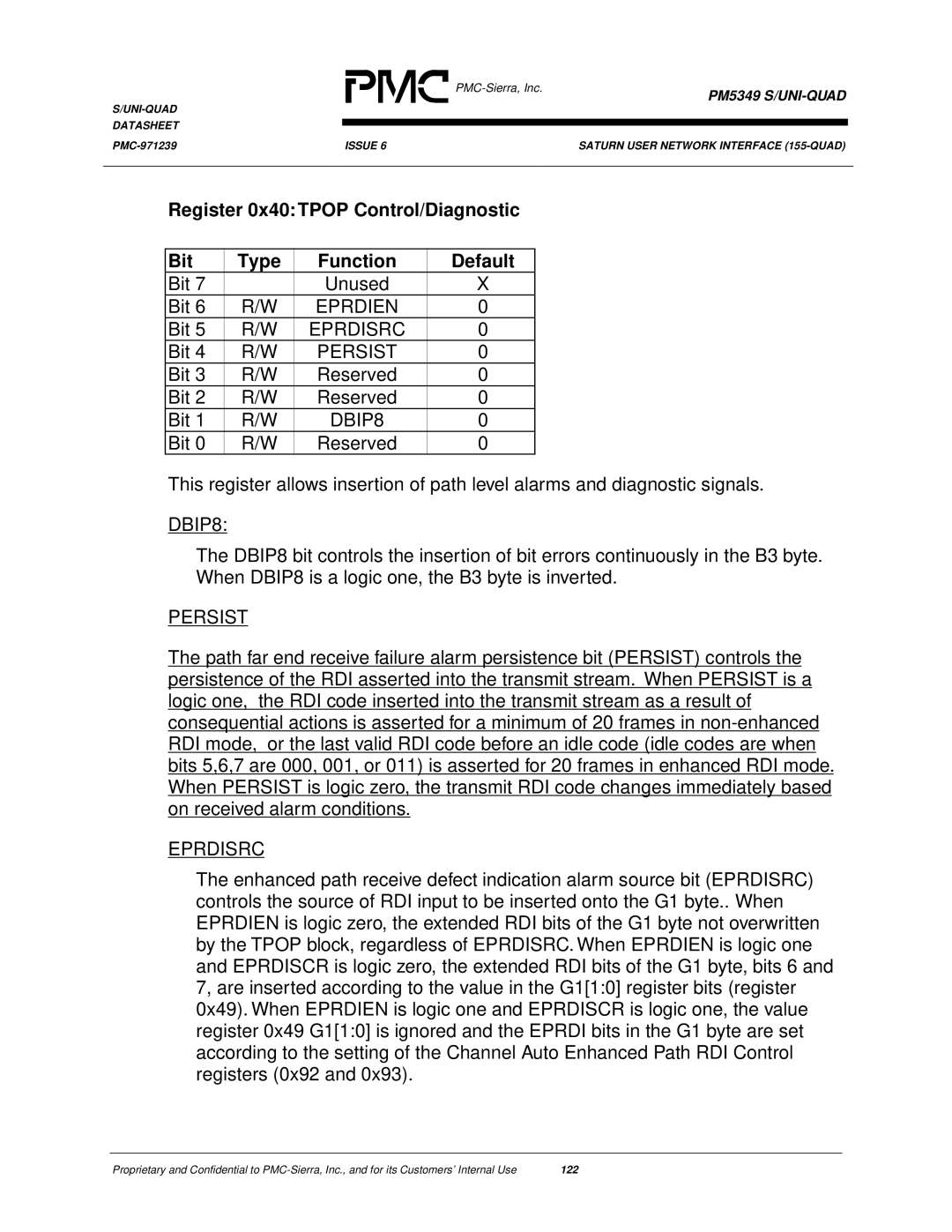

Register 0x40: TPOP Control/Diagnostic

Bit | Type | Function | Default |

Bit 7 |

| Unused | X |

Bit 6 | R/W | EPRDIEN | 0 |

Bit 5 | R/W | EPRDISRC | 0 |

Bit 4 | R/W | PERSIST | 0 |

Bit 3 | R/W | Reserved | 0 |

Bit 2 | R/W | Reserved | 0 |

Bit 1 | R/W | DBIP8 | 0 |

Bit 0 | R/W | Reserved | 0 |

This register allows insertion of path level alarms and diagnostic signals.

DBIP8:

The DBIP8 bit controls the insertion of bit errors continuously in the B3 byte. When DBIP8 is a logic one, the B3 byte is inverted.

PERSIST

The path far end receive failure alarm persistence bit (PERSIST) controls the persistence of the RDI asserted into the transmit stream. When PERSIST is a logic one, the RDI code inserted into the transmit stream as a result of consequential actions is asserted for a minimum of 20 frames in

EPRDISRC

The enhanced path receive defect indication alarm source bit (EPRDISRC) controls the source of RDI input to be inserted onto the G1 byte.. When EPRDIEN is logic zero, the extended RDI bits of the G1 byte not overwritten by the TPOP block, regardless of EPRDISRC. When EPRDIEN is logic one and EPRDISCR is logic zero, the extended RDI bits of the G1 byte, bits 6 and 7, are inserted according to the value in the G1[1:0] register bits (register 0x49). When EPRDIEN is logic one and EPRDISCR is logic one, the value register 0x49 G1[1:0] is ignored and the EPRDI bits in the G1 byte are set according to the setting of the Channel Auto Enhanced Path RDI Control registers (0x92 and 0x93).

Proprietary and Confidential to | 122 |