DATASHEET

PM5349 S/UNI-QUAD

ISSUE 6 | SATURN USER NETWORK INTERFACE | |

|

|

|

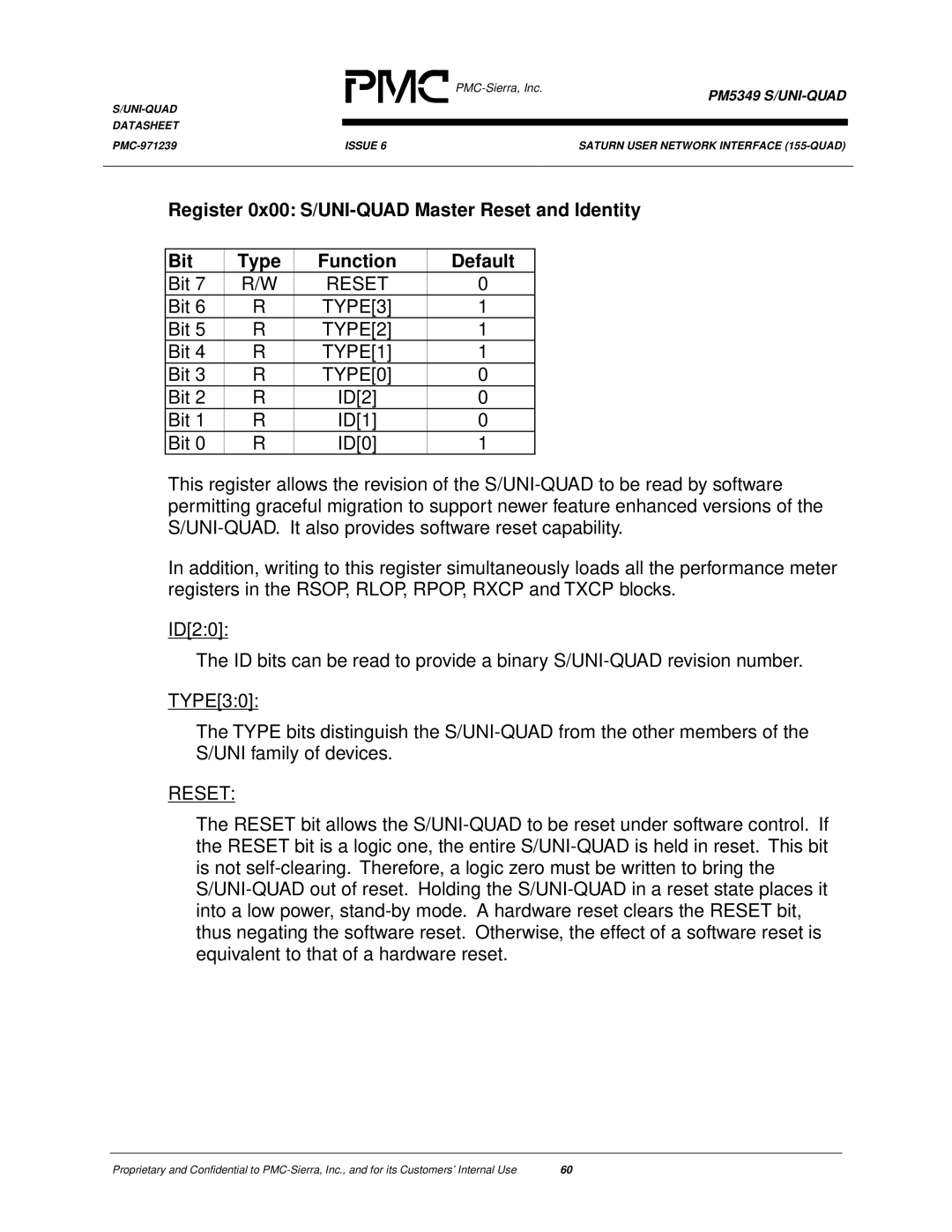

Register 0x00:

Bit | Type | Function | Default |

Bit 7 | R/W | RESET | 0 |

Bit 6 | R | TYPE[3] | 1 |

Bit 5 | R | TYPE[2] | 1 |

Bit 4 | R | TYPE[1] | 1 |

Bit 3 | R | TYPE[0] | 0 |

Bit 2 | R | ID[2] | 0 |

Bit 1 | R | ID[1] | 0 |

Bit 0 | R | ID[0] | 1 |

This register allows the revision of the

In addition, writing to this register simultaneously loads all the performance meter registers in the RSOP, RLOP, RPOP, RXCP and TXCP blocks.

ID[2:0]:

The ID bits can be read to provide a binary

TYPE[3:0]:

The TYPE bits distinguish the

RESET:

The RESET bit allows the

Proprietary and Confidential to | 60 |