DATASHEET

PM5349 S/UNI-QUAD

ISSUE 6 | SATURN USER NETWORK INTERFACE | |

|

|

|

12 TEST FEATURES DESCRIPTION

Simultaneously asserting (low) the CSB, RDB and WRB inputs causes all digital output pins and the data bus to be held in a

Test mode registers are used to apply test vectors during production testing of the

Test mode registers may also be used for board testing. When all of the TSBs within the

In addition, the

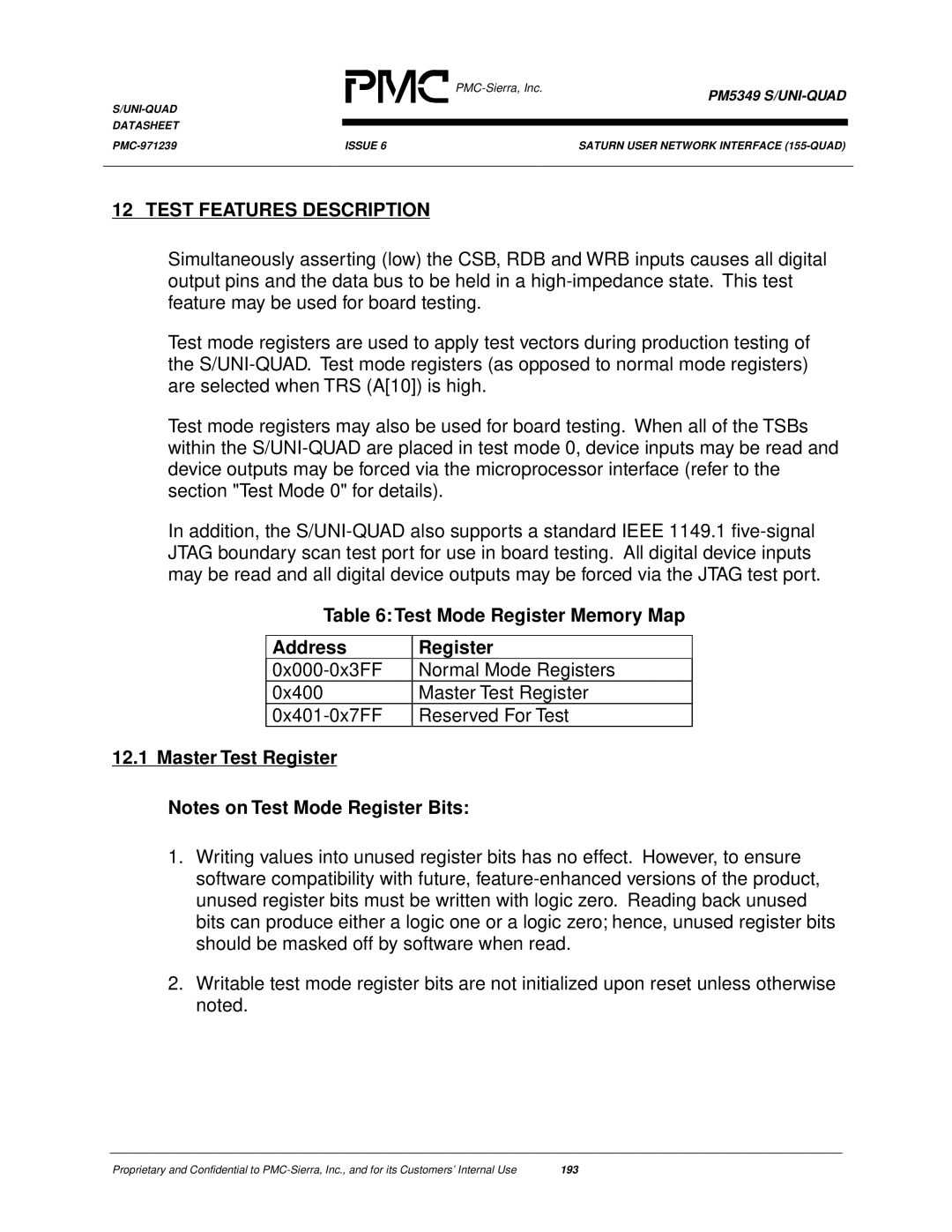

Table 6: Test Mode Register Memory Map

Address | Register |

Normal Mode Registers | |

0x400 | Master Test Register |

Reserved For Test |

12.1 Master Test Register

Notes on Test Mode Register Bits:

1.Writing values into unused register bits has no effect. However, to ensure software compatibility with future,

2.Writable test mode register bits are not initialized upon reset unless otherwise noted.

Proprietary and Confidential to | 193 |