|

| PM5349 |

| |

|

|

| ||

|

|

|

| |

DATASHEET |

|

|

|

|

|

|

|

| |

|

|

|

| |

ISSUE 6 |

| SATURN USER NETWORK INTERFACE |

| |

|

|

|

|

|

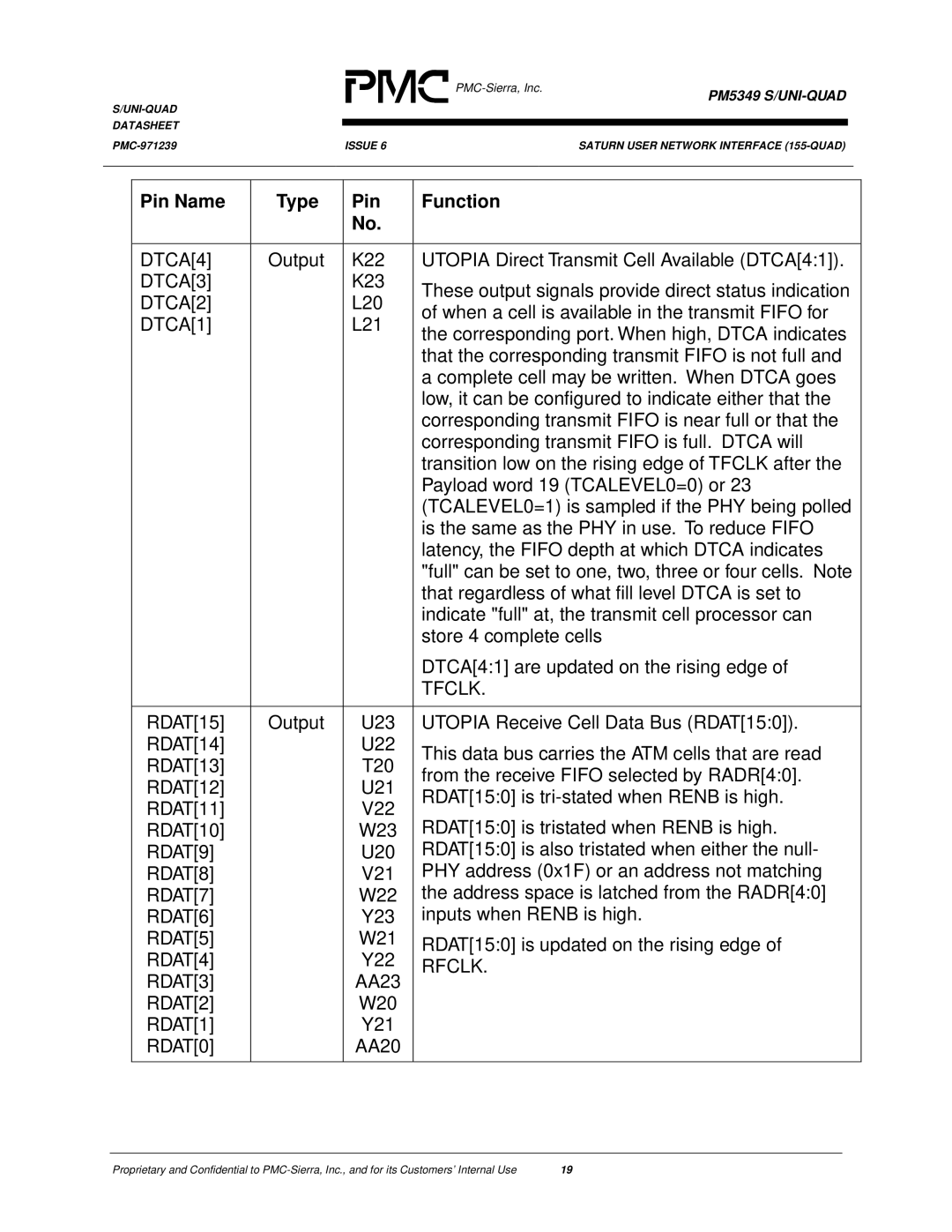

Pin Name | Type | Pin | Function |

|

| No. |

|

|

|

|

|

DTCA[4] | Output | K22 | UTOPIA Direct Transmit Cell Available (DTCA[4:1]). |

DTCA[3] |

| K23 | These output signals provide direct status indication |

DTCA[2] |

| L20 | |

| of when a cell is available in the transmit FIFO for | ||

DTCA[1] |

| L21 | |

| the corresponding port. When high, DTCA indicates | ||

|

|

| |

|

|

| that the corresponding transmit FIFO is not full and |

|

|

| a complete cell may be written. When DTCA goes |

|

|

| low, it can be configured to indicate either that the |

|

|

| corresponding transmit FIFO is near full or that the |

|

|

| corresponding transmit FIFO is full. DTCA will |

|

|

| transition low on the rising edge of TFCLK after the |

|

|

| Payload word 19 (TCALEVEL0=0) or 23 |

|

|

| (TCALEVEL0=1) is sampled if the PHY being polled |

|

|

| is the same as the PHY in use. To reduce FIFO |

|

|

| latency, the FIFO depth at which DTCA indicates |

|

|

| "full" can be set to one, two, three or four cells. Note |

|

|

| that regardless of what fill level DTCA is set to |

|

|

| indicate "full" at, the transmit cell processor can |

|

|

| store 4 complete cells |

|

|

| DTCA[4:1] are updated on the rising edge of |

|

|

| TFCLK. |

|

|

|

|

RDAT[15] | Output | U23 | UTOPIA Receive Cell Data Bus (RDAT[15:0]). |

RDAT[14] |

| U22 | This data bus carries the ATM cells that are read |

RDAT[13] |

| T20 | |

| from the receive FIFO selected by RADR[4:0]. | ||

RDAT[12] |

| U21 | |

| RDAT[15:0] is | ||

RDAT[11] |

| V22 | |

| RDAT[15:0] is tristated when RENB is high. | ||

RDAT[10] |

| W23 | |

RDAT[9] |

| U20 | RDAT[15:0] is also tristated when either the null- |

RDAT[8] |

| V21 | PHY address (0x1F) or an address not matching |

RDAT[7] |

| W22 | the address space is latched from the RADR[4:0] |

RDAT[6] |

| Y23 | inputs when RENB is high. |

RDAT[5] |

| W21 | RDAT[15:0] is updated on the rising edge of |

RDAT[4] |

| Y22 | |

| RFCLK. | ||

RDAT[3] |

| AA23 | |

|

| ||

RDAT[2] |

| W20 |

|

RDAT[1] |

| Y21 |

|

RDAT[0] |

| AA20 |

|

|

|

|

|

Proprietary and Confidential to | 19 |