DATASHEET

PM5349 S/UNI-QUAD

ISSUE 6 | SATURN USER NETWORK INTERFACE | |

|

|

|

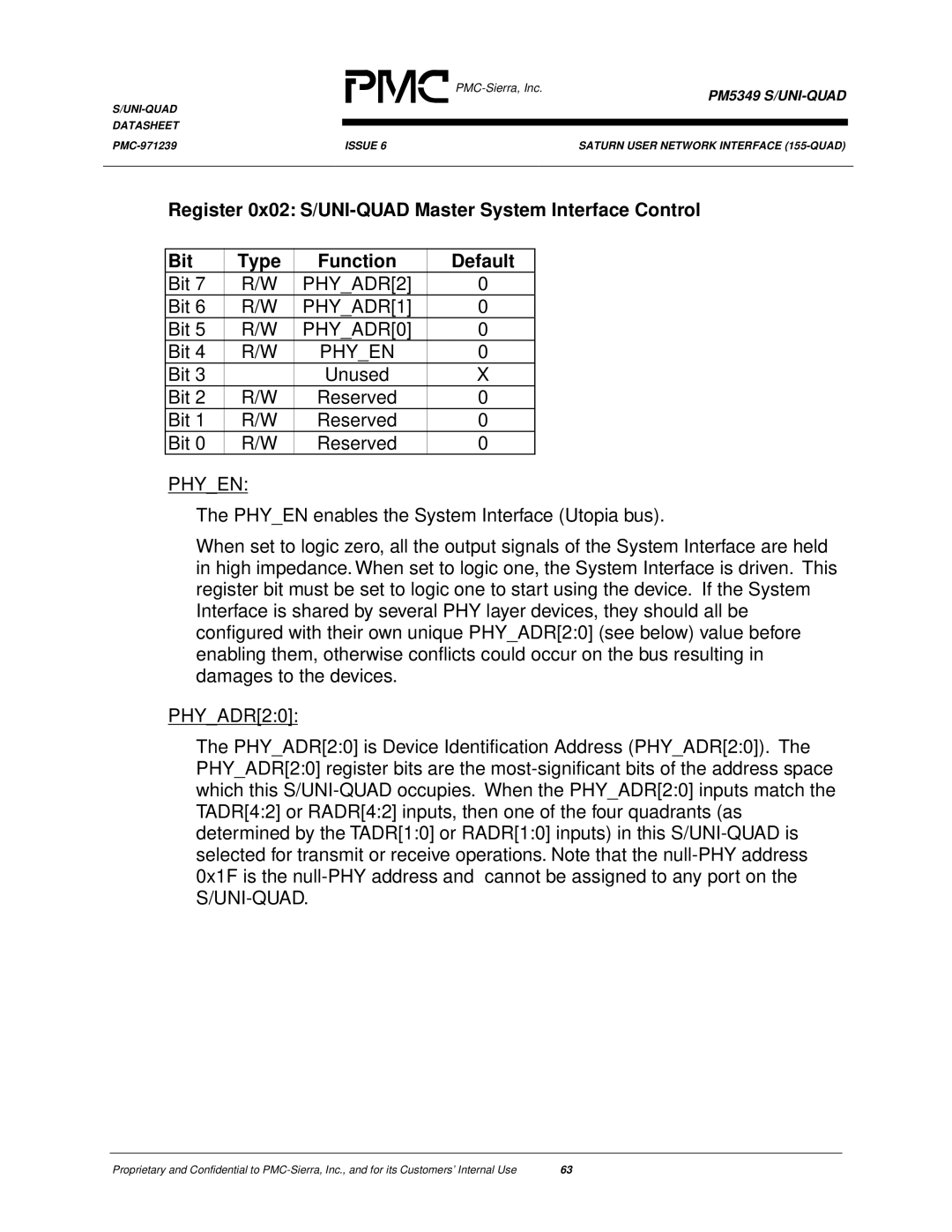

Register 0x02:

Bit | Type | Function | Default |

Bit 7 | R/W | PHY_ADR[2] | 0 |

Bit 6 | R/W | PHY_ADR[1] | 0 |

Bit 5 | R/W | PHY_ADR[0] | 0 |

Bit 4 | R/W | PHY_EN | 0 |

Bit 3 |

| Unused | X |

Bit 2 | R/W | Reserved | 0 |

Bit 1 | R/W | Reserved | 0 |

Bit 0 | R/W | Reserved | 0 |

PHY_EN:

The PHY_EN enables the System Interface (Utopia bus).

When set to logic zero, all the output signals of the System Interface are held in high impedance. When set to logic one, the System Interface is driven. This register bit must be set to logic one to start using the device. If the System Interface is shared by several PHY layer devices, they should all be configured with their own unique PHY_ADR[2:0] (see below) value before enabling them, otherwise conflicts could occur on the bus resulting in damages to the devices.

PHY_ADR[2:0]:

The PHY_ADR[2:0] is Device Identification Address (PHY_ADR[2:0]). The PHY_ADR[2:0] register bits are the

Proprietary and Confidential to | 63 |