DATASHEET

PM5349 S/UNI-QUAD

ISSUE 6 | SATURN USER NETWORK INTERFACE | |

|

|

|

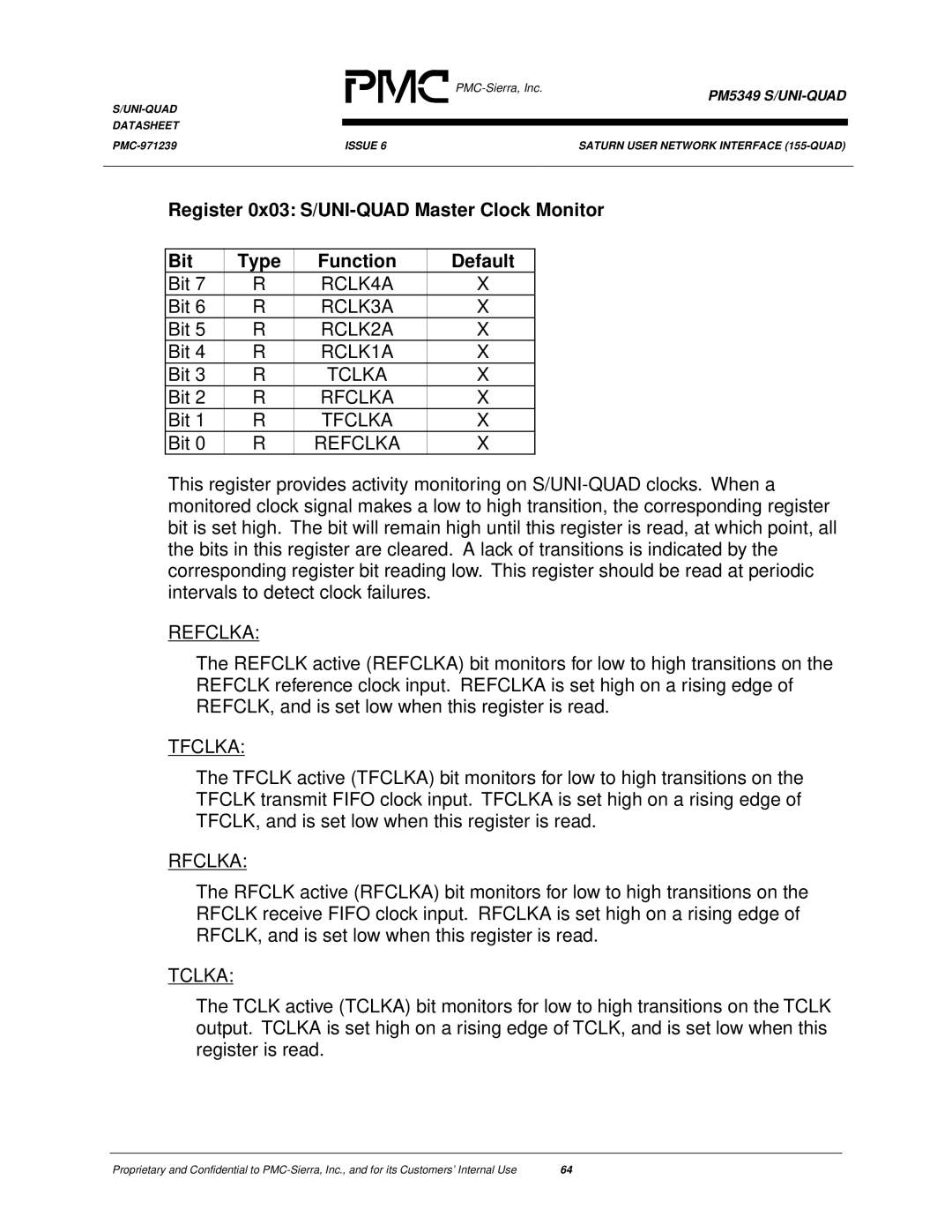

Register 0x03:

Bit | Type | Function | Default |

Bit 7 | R | RCLK4A | X |

Bit 6 | R | RCLK3A | X |

Bit 5 | R | RCLK2A | X |

Bit 4 | R | RCLK1A | X |

Bit 3 | R | TCLKA | X |

Bit 2 | R | RFCLKA | X |

Bit 1 | R | TFCLKA | X |

Bit 0 | R | REFCLKA | X |

This register provides activity monitoring on

REFCLKA:

The REFCLK active (REFCLKA) bit monitors for low to high transitions on the REFCLK reference clock input. REFCLKA is set high on a rising edge of REFCLK, and is set low when this register is read.

TFCLKA:

The TFCLK active (TFCLKA) bit monitors for low to high transitions on the TFCLK transmit FIFO clock input. TFCLKA is set high on a rising edge of TFCLK, and is set low when this register is read.

RFCLKA:

The RFCLK active (RFCLKA) bit monitors for low to high transitions on the RFCLK receive FIFO clock input. RFCLKA is set high on a rising edge of RFCLK, and is set low when this register is read.

TCLKA:

The TCLK active (TCLKA) bit monitors for low to high transitions on the TCLK output. TCLKA is set high on a rising edge of TCLK, and is set low when this register is read.

Proprietary and Confidential to | 64 |