DATASHEET

PM5349 S/UNI-QUAD

ISSUE 6 | SATURN USER NETWORK INTERFACE | |

|

|

|

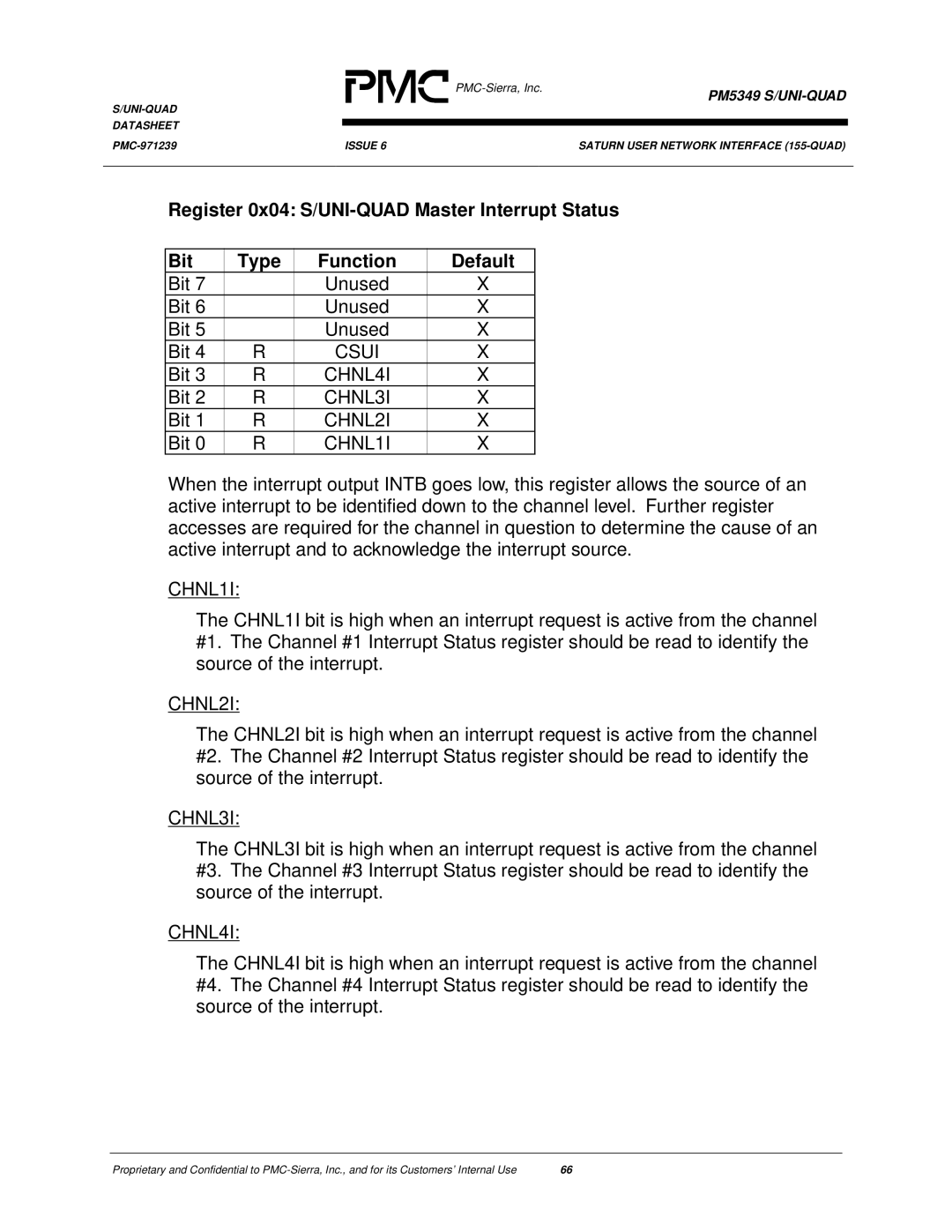

Register 0x04:

Bit | Type | Function | Default |

Bit 7 |

| Unused | X |

Bit 6 |

| Unused | X |

Bit 5 |

| Unused | X |

Bit 4 | R | CSUI | X |

Bit 3 | R | CHNL4I | X |

Bit 2 | R | CHNL3I | X |

Bit 1 | R | CHNL2I | X |

Bit 0 | R | CHNL1I | X |

When the interrupt output INTB goes low, this register allows the source of an active interrupt to be identified down to the channel level. Further register accesses are required for the channel in question to determine the cause of an active interrupt and to acknowledge the interrupt source.

CHNL1I:

The CHNL1I bit is high when an interrupt request is active from the channel #1. The Channel #1 Interrupt Status register should be read to identify the source of the interrupt.

CHNL2I:

The CHNL2I bit is high when an interrupt request is active from the channel #2. The Channel #2 Interrupt Status register should be read to identify the source of the interrupt.

CHNL3I:

The CHNL3I bit is high when an interrupt request is active from the channel #3. The Channel #3 Interrupt Status register should be read to identify the source of the interrupt.

CHNL4I:

The CHNL4I bit is high when an interrupt request is active from the channel #4. The Channel #4 Interrupt Status register should be read to identify the source of the interrupt.

Proprietary and Confidential to | 66 |