DATASHEET

PM5349 S/UNI-QUAD

ISSUE 6 | SATURN USER NETWORK INTERFACE | |

|

|

|

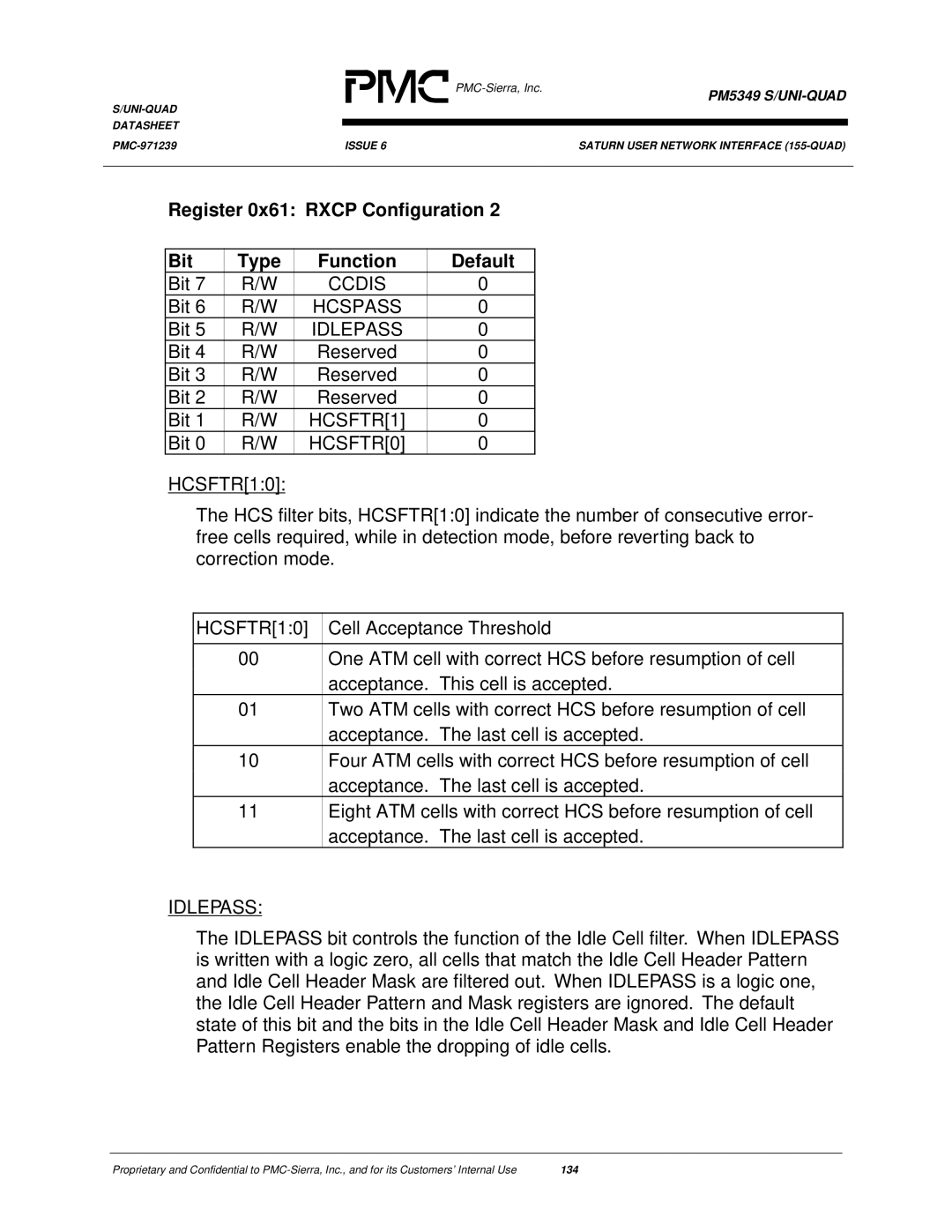

Register 0x61: RXCP Configuration 2

Bit | Type | Function | Default |

Bit 7 | R/W | CCDIS | 0 |

Bit 6 | R/W | HCSPASS | 0 |

Bit 5 | R/W | IDLEPASS | 0 |

Bit 4 | R/W | Reserved | 0 |

Bit 3 | R/W | Reserved | 0 |

Bit 2 | R/W | Reserved | 0 |

Bit 1 | R/W | HCSFTR[1] | 0 |

Bit 0 | R/W | HCSFTR[0] | 0 |

HCSFTR[1:0]:

The HCS filter bits, HCSFTR[1:0] indicate the number of consecutive error- free cells required, while in detection mode, before reverting back to correction mode.

HCSFTR[1:0] Cell Acceptance Threshold

00One ATM cell with correct HCS before resumption of cell acceptance. This cell is accepted.

01Two ATM cells with correct HCS before resumption of cell acceptance. The last cell is accepted.

10Four ATM cells with correct HCS before resumption of cell acceptance. The last cell is accepted.

11Eight ATM cells with correct HCS before resumption of cell acceptance. The last cell is accepted.

IDLEPASS:

The IDLEPASS bit controls the function of the Idle Cell filter. When IDLEPASS is written with a logic zero, all cells that match the Idle Cell Header Pattern and Idle Cell Header Mask are filtered out. When IDLEPASS is a logic one, the Idle Cell Header Pattern and Mask registers are ignored. The default state of this bit and the bits in the Idle Cell Header Mask and Idle Cell Header Pattern Registers enable the dropping of idle cells.

Proprietary and Confidential to | 134 |