DATASHEET

PM5349 S/UNI-QUAD

ISSUE 6 | SATURN USER NETWORK INTERFACE | |

|

|

|

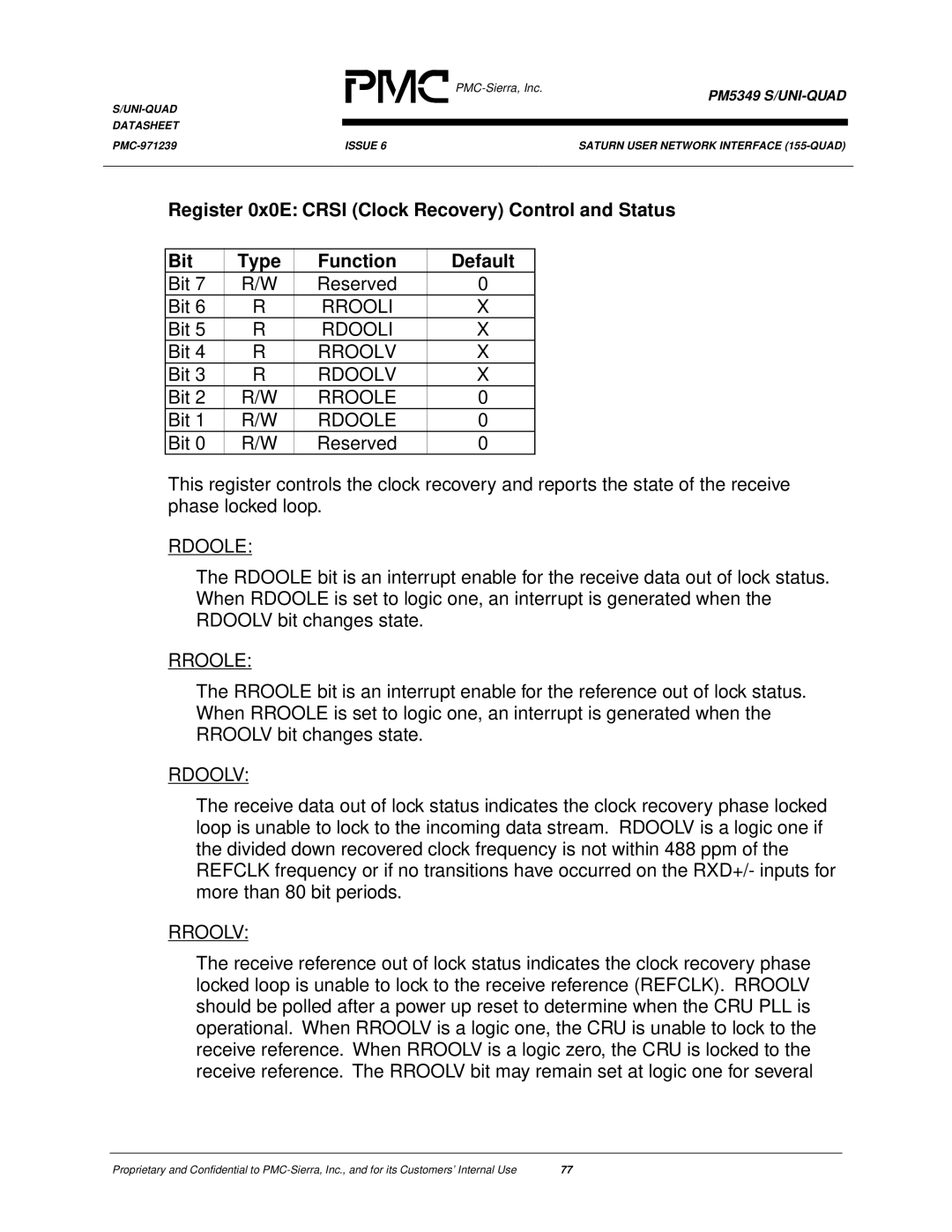

Register 0x0E: CRSI (Clock Recovery) Control and Status

Bit | Type | Function | Default |

Bit 7 | R/W | Reserved | 0 |

Bit 6 | R | RROOLI | X |

Bit 5 | R | RDOOLI | X |

Bit 4 | R | RROOLV | X |

Bit 3 | R | RDOOLV | X |

Bit 2 | R/W | RROOLE | 0 |

Bit 1 | R/W | RDOOLE | 0 |

Bit 0 | R/W | Reserved | 0 |

This register controls the clock recovery and reports the state of the receive phase locked loop.

RDOOLE:

The RDOOLE bit is an interrupt enable for the receive data out of lock status. When RDOOLE is set to logic one, an interrupt is generated when the RDOOLV bit changes state.

RROOLE:

The RROOLE bit is an interrupt enable for the reference out of lock status. When RROOLE is set to logic one, an interrupt is generated when the RROOLV bit changes state.

RDOOLV:

The receive data out of lock status indicates the clock recovery phase locked loop is unable to lock to the incoming data stream. RDOOLV is a logic one if the divided down recovered clock frequency is not within 488 ppm of the REFCLK frequency or if no transitions have occurred on the RXD+/- inputs for more than 80 bit periods.

RROOLV:

The receive reference out of lock status indicates the clock recovery phase locked loop is unable to lock to the receive reference (REFCLK). RROOLV should be polled after a power up reset to determine when the CRU PLL is operational. When RROOLV is a logic one, the CRU is unable to lock to the receive reference. When RROOLV is a logic zero, the CRU is locked to the receive reference. The RROOLV bit may remain set at logic one for several

Proprietary and Confidential to | 77 |