DATASHEET

PM5349 S/UNI-QUAD

ISSUE 6 | SATURN USER NETWORK INTERFACE | |

|

|

|

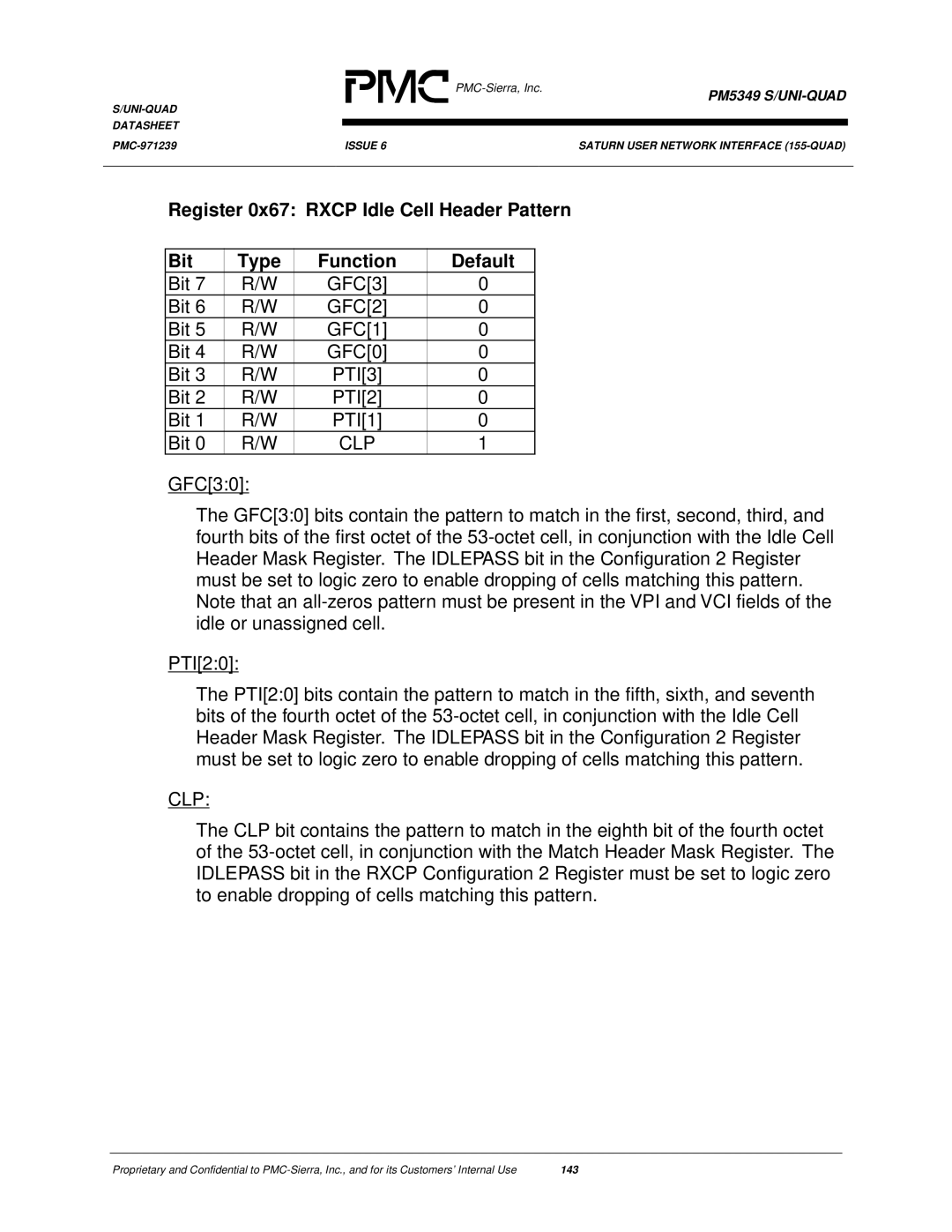

Register 0x67: RXCP Idle Cell Header Pattern

Bit | Type | Function | Default |

Bit 7 | R/W | GFC[3] | 0 |

Bit 6 | R/W | GFC[2] | 0 |

Bit 5 | R/W | GFC[1] | 0 |

Bit 4 | R/W | GFC[0] | 0 |

Bit 3 | R/W | PTI[3] | 0 |

Bit 2 | R/W | PTI[2] | 0 |

Bit 1 | R/W | PTI[1] | 0 |

Bit 0 | R/W | CLP | 1 |

GFC[3:0]:

The GFC[3:0] bits contain the pattern to match in the first, second, third, and fourth bits of the first octet of the

PTI[2:0]:

The PTI[2:0] bits contain the pattern to match in the fifth, sixth, and seventh bits of the fourth octet of the

CLP:

The CLP bit contains the pattern to match in the eighth bit of the fourth octet of the

Proprietary and Confidential to | 143 |