DATASHEET

PM5349 S/UNI-QUAD

ISSUE 6 | SATURN USER NETWORK INTERFACE | |

|

|

|

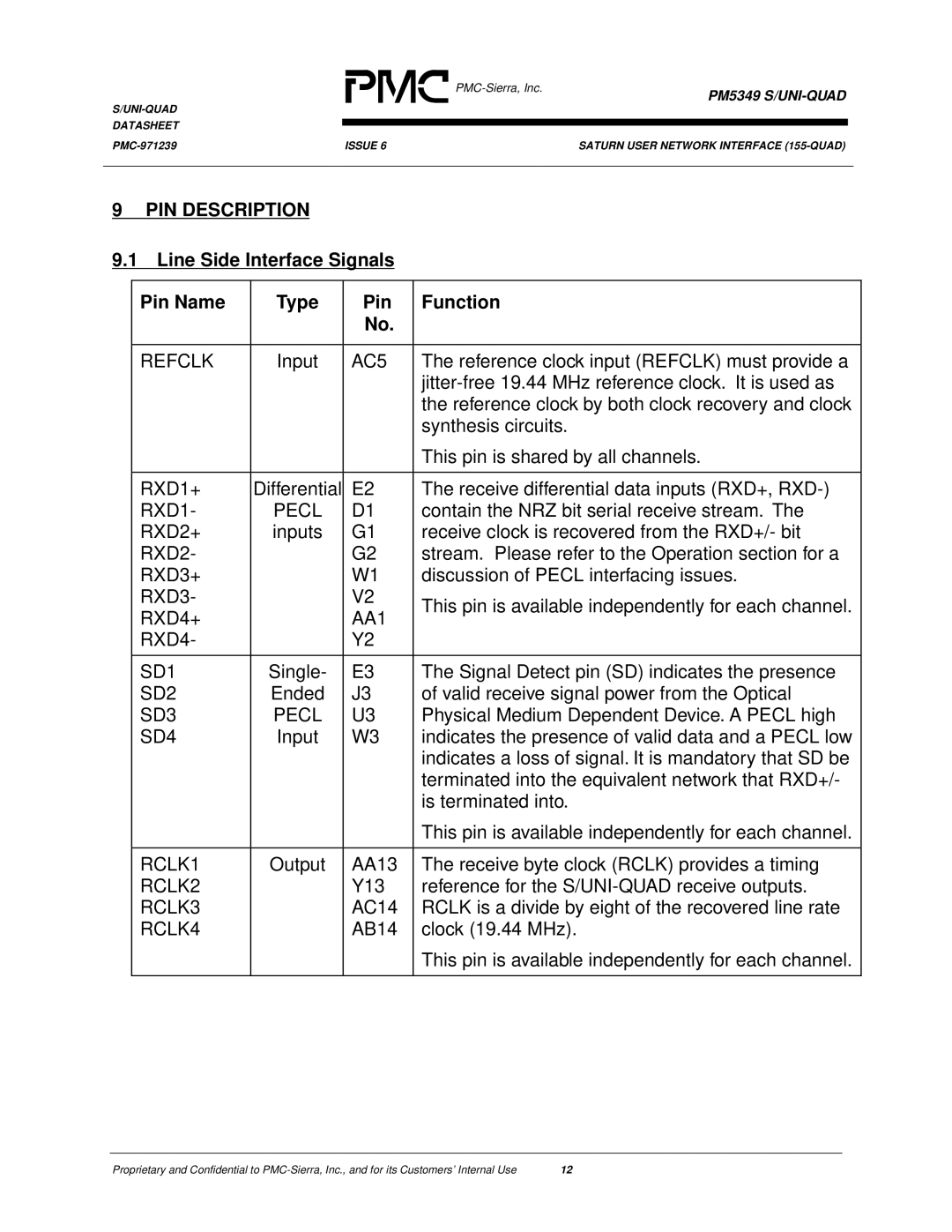

9 PIN DESCRIPTION

9.1Line Side Interface Signals

Pin Name | Type | Pin | Function |

|

| No. |

|

|

|

|

|

REFCLK | Input | AC5 | The reference clock input (REFCLK) must provide a |

|

|

| |

|

|

| the reference clock by both clock recovery and clock |

|

|

| synthesis circuits. |

|

|

| This pin is shared by all channels. |

|

|

|

|

RXD1+ | Differential | E2 | The receive differential data inputs (RXD+, |

RXD1- | PECL | D1 | contain the NRZ bit serial receive stream. The |

RXD2+ | inputs | G1 | receive clock is recovered from the RXD+/- bit |

RXD2- |

| G2 | stream. Please refer to the Operation section for a |

RXD3+ |

| W1 | discussion of PECL interfacing issues. |

RXD3- |

| V2 | This pin is available independently for each channel. |

RXD4+ |

| AA1 | |

|

| ||

RXD4- |

| Y2 |

|

|

|

|

|

SD1 | Single- | E3 | The Signal Detect pin (SD) indicates the presence |

SD2 | Ended | J3 | of valid receive signal power from the Optical |

SD3 | PECL | U3 | Physical Medium Dependent Device. A PECL high |

SD4 | Input | W3 | indicates the presence of valid data and a PECL low |

|

|

| indicates a loss of signal. It is mandatory that SD be |

|

|

| terminated into the equivalent network that RXD+/- |

|

|

| is terminated into. |

|

|

| This pin is available independently for each channel. |

|

|

|

|

RCLK1 | Output | AA13 | The receive byte clock (RCLK) provides a timing |

RCLK2 |

| Y13 | reference for the |

RCLK3 |

| AC14 | RCLK is a divide by eight of the recovered line rate |

RCLK4 |

| AB14 | clock (19.44 MHz). |

|

|

| This pin is available independently for each channel. |

|

|

|

|

Proprietary and Confidential to | 12 |