Apx. C Pin Assignments | Appendices |

Appendix C Pin Assignments

System Board

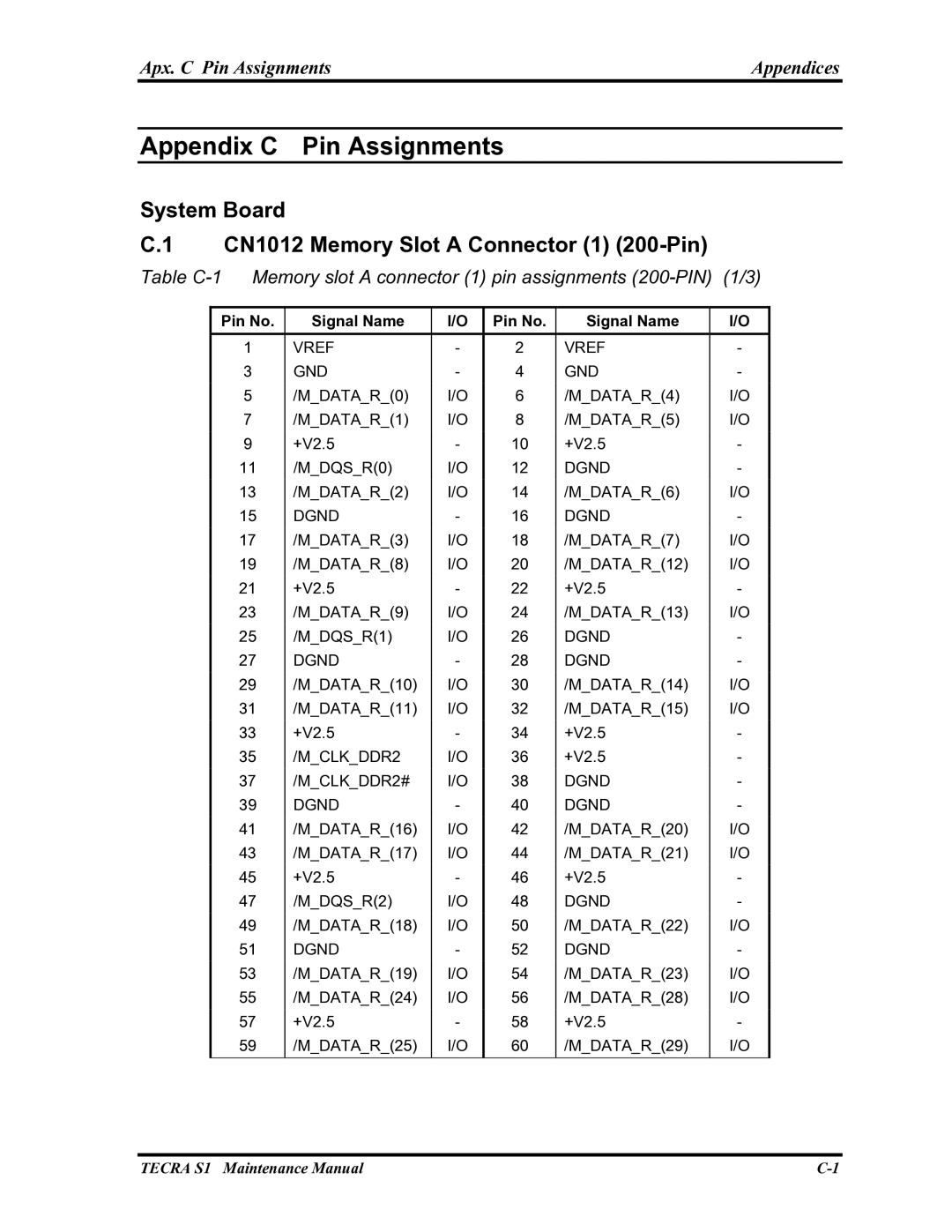

C.1 CN1012 Memory Slot A Connector (1) (200-Pin)

Table

Pin No. | Signal Name | I/O | Pin No. | Signal Name | I/O |

1 | VREF | - | 2 | VREF | - |

3 | GND | - | 4 | GND | - |

5 | /M_DATA_R_(0) | I/O | 6 | /M_DATA_R_(4) | I/O |

7 | /M_DATA_R_(1) | I/O | 8 | /M_DATA_R_(5) | I/O |

9 | +V2.5 | - | 10 | +V2.5 | - |

11 | /M_DQS_R(0) | I/O | 12 | DGND | - |

13 | /M_DATA_R_(2) | I/O | 14 | /M_DATA_R_(6) | I/O |

15 | DGND | - | 16 | DGND | - |

17 | /M_DATA_R_(3) | I/O | 18 | /M_DATA_R_(7) | I/O |

19 | /M_DATA_R_(8) | I/O | 20 | /M_DATA_R_(12) | I/O |

21 | +V2.5 | - | 22 | +V2.5 | - |

23 | /M_DATA_R_(9) | I/O | 24 | /M_DATA_R_(13) | I/O |

25 | /M_DQS_R(1) | I/O | 26 | DGND | - |

27 | DGND | - | 28 | DGND | - |

29 | /M_DATA_R_(10) | I/O | 30 | /M_DATA_R_(14) | I/O |

31 | /M_DATA_R_(11) | I/O | 32 | /M_DATA_R_(15) | I/O |

33 | +V2.5 | - | 34 | +V2.5 | - |

35 | /M_CLK_DDR2 | I/O | 36 | +V2.5 | - |

37 | /M_CLK_DDR2# | I/O | 38 | DGND | - |

39 | DGND | - | 40 | DGND | - |

41 | /M_DATA_R_(16) | I/O | 42 | /M_DATA_R_(20) | I/O |

43 | /M_DATA_R_(17) | I/O | 44 | /M_DATA_R_(21) | I/O |

45 | +V2.5 | - | 46 | +V2.5 | - |

47 | /M_DQS_R(2) | I/O | 48 | DGND | - |

49 | /M_DATA_R_(18) | I/O | 50 | /M_DATA_R_(22) | I/O |

51 | DGND | - | 52 | DGND | - |

53 | /M_DATA_R_(19) | I/O | 54 | /M_DATA_R_(23) | I/O |

55 | /M_DATA_R_(24) | I/O | 56 | /M_DATA_R_(28) | I/O |

57 | +V2.5 | - | 58 | +V2.5 | - |

59 | /M_DATA_R_(25) | I/O | 60 | /M_DATA_R_(29) | I/O |

TECRA S1 Maintenance Manual |