Agilent Technologies. All rights reserved

Agilent Technologies 16760A Logic Analyzer

Probing

Captures input signals as low as 200 mV p-p

Sampling Mode on

Agilent Technologies 16760A Logic Analyzer

Concepts on

Reference on

Glossary see

See Also

Contents

Choosing the Sampling Mode

114

Using Symbols 101

110

112

Format Tab 174

Displaying Captured Eye Scan Data

152

155

Eye Scan Tab 204

210

211

Specifications and Characteristics

240

259

Glossary Index

Contents

Getting Started

Eye scan sampling mode, measurements will have these steps

Probing and Sampling Mode Selection Steps

Next . Choose the sampling mode on

Connect logic analyzer to the device under test

To choose the sampling mode

Choose the sampling mode

If you chose State Mode

If you chose Timing Mode

Next . Format labels for the probed signals on

Either Timing Mode or State Mode

If you chose Eye Scan Mode

Format labels for the probed signals

To specify threshold voltages

To assign pods to the logic analyzer

Next

Defined threshold voltage Select the Close button

To assign names to logic analyzer channels

Define the trigger condition

Timing Mode or State Mode Steps

Next . Run the measurement on

Run the measurement

Display the captured data

Next . Display the captured data on

To open Waveform or Listing displays

To add display tools via the Workspace window

Next For More Information... on

Select channels for the eye scan measurement

Eye Scan Mode Steps

Next . Set the eye scan range and resolution on

Set the eye scan range and resolution

Next . Run the eye scan measurement on

Run the eye scan measurement

Next . Display the captured eye scan data on

Display the captured eye scan data

Eye Scan display window, use the following subtabs

For More Information

For More Information

Probing and Selecting the Sampling Mode

Probing and Selecting the Sampling Mode

Probing the Device Under Test

Using the E5378A Single-Ended Probe

Either

Single-ended signal

Number

Numbers

Using the E5379A Differential Probe

Reference voltage

Or single-ended signals

Independent threshold adjustment

Negative data inputs

Or AMP

Using the E5380A Mictor-Compatible Probe

Using the E5382A Single-ended Flying Lead Probe Set

Additional Accessories

Using an Analysis Probe

Probing the Device Under Test

Selecting the Timing Mode Asynchronous Sampling

Choosing the Sampling Mode

To select the conventional/transitional configuration

To select the timing mode

Sample rate is the inverse of the sample period

To specify the sample period

To manually adjust sampling positions on

Selecting the State Mode Synchronous Sampling

State Mode Sampling Position

To automatically adjust sampling positions on

To select the state speed configuration

To select the state mode

For the clock input signal that will be used

To set up the sampling clock

To automatically adjust sampling positions

Automatically sets the sampling position

Run simultaneously

To run eye finder repetitively

Choose the labels that you wish to run eye finder on

To view eye finder data as a bus composite

To view eye finder data as a stack of channels

To save/load eye finder data

To manually adjust sampling positions

Eye Finder Advanced Settings Dialog on

Eye finder data must be saved and loaded separately

Either Timing Mode or State Mode

To specify the trigger position

To set acquisition memory depth

You can also name analyzers in the Pod Assignment Dialog on

To name an analyzer

To turn an analyzer off or on

You can give more descriptive names to a logic analyzer

High-speed or high-bandwidth oscilloscope

Selecting the Eye Scan Mode

To select the eye scan mode

To select the eye scan mode speed configuration

To set up the eye scan mode reference clock

Format tab has activity indicators that show signal levels

Formatting Labels for Logic Analyzer Probes

To assign pods to the analyzer

Capturing Data on 17 Channels in State Mode

To set up qualified eye scan measurements on

To set pod threshold voltages

To set clock threshold voltages

To assign probe channels to labels

Maximum of 32 channels can be assigned to a label

Label off

To delete labels

Label

Signals

To import label names and assignments from a netlist

E5378A and E5380A probe types to be selectable

To import label definitions from an Ascii file

To assign label name Blue to channel 5 on pod A2

Label Definition File Format Examples

To export label definitions to an Ascii file

To change the label polarity

Channel 5 on pod A2, and channel 6 on pod A1

To reorder bits in a label

Changing the label polarity will have the following effects

Changing the label polarity does not affect

To display a label that was off

To turn labels off or on

To turn a label off

To turn a label on

Using the Logic Analyzer in Timing or State Mode

Using the Logic Analyzer in Timing or State Mode

Setting Up Triggers and Running Measurements

Use trigger functions for basic measurements

General

To select a trigger function

Using Trigger Functions

To specify a label pattern event Timing only

To specify a label edge event

To enter symbolic label values on Symbols Selector Dialog on

To compress a trigger function

To expand a trigger function

To copy trigger function libraries between systems

To load/unload trigger function libraries

To count time, states, or turn counting off

Using Other Trigger Features

If you chose Custom

To specify default storing

To assign pods to the analyzer on

Reduced by half in order to store the required time tags

To clear default storing changes

Acquisition option button and choose either On or Off

Default storing is initially on or off

Trigger tabs Default Storing subtab, select the At start

To insert a store action state mode on

To replace sequence levels

To insert/replace/delete sequence levels

To clear the trigger sequence on

To insert sequence levels

To cut/copy-and-paste sequence levels

Setting Up Triggers and Running Measurements

Example system14 Slot C Analyzer C has triggered

Trigger tab, select the Overview subtab

To restore default trigger settings

To view a picture of the trigger sequence

To clear the trigger sequence

To specify a time duration for events timing only

To specify a duration or occurrence count for events

Available

To insert a store action state mode

To insert timer actions/events

To insert a timer action

To insert a counter event

To insert a timer event

To insert counter actions/events

To insert a counter action

To insert flag actions/events

To insert a flag event

To drive the Port Out signal with a flag

To insert a reset occurrence counter action

To group events

To use named events

To insert a named event

Saving/Recalling Trigger Setups

To save a trigger setup

To give an event list a name

To start/stop measurements

To recall a trigger setup

Running Measurements

To clear the trigger save/recall list

Waiting for Trigger on

If nothing happens when you start a measurement

To stop a measurement

Select the Stop or Stop All button

To view the trigger status

To open Waveform or Listing displays

Displaying Captured Data

Search for particular data values captured on labels

Help volume

To use other display tools

Windows

Displaying Captured Data

Into parallel words which are easier to view and analyze

Analyzer help volume

Intermittent Data Errors Unwanted Triggers

If the captured data doesnt look correct

This situation will occur in these cases

If there are filtered data holes in display memory

To display symbols for data values

To view symbolic values in a waveform display

To view symbolic values in a listing display

To cancel the display processing of captured data

Select the Cancel button

100

Using Symbols

You can use symbol names in place of data values when

101

To load object file symbols

To reload object file symbols

102

Object file symbols are reloaded

To adjust symbol values for relocated code

104

To create user-defined symbols

Whose symbols you wish to relocate

To replace user-defined symbols

To load user-defined symbols

To enter symbolic label values

When entering label values in the trigger sequence

To delete user-defined symbols

To create an Ascii symbol file

General-Purpose Ascii GPA Symbol File Format on

106

Create the reader.ini file on your workstation or PC

Examples Example for Elf/Stabs

StabsType

ReadOnlyTicoffPage

AppendTicoffPage

Example for Coff/Stabs using Ticoff reader

Example for Ticoff

109

You can print captured data from display tool windows

Printing/Exporting Captured Data

111

Select the file name and automatic file sequencing options

Select the Read File button

Icon to view the imported data

Cross-Triggering

To cross-trigger with another instrument

112

113

When the logic analyzer drives the arm signal

114

Solving Logic Analysis Problems

To test the logic analyzer hardware

To test the logic analyzer hardware on

Service Center for assistance

System help volume

115

116

Saving and Loading Logic Analyzer Configurations

To save logic analyzer configurations

To load logic analyzer configurations

117

Using the Logic Analyzer in Eye Scan Mode

118

119

Setting Up and Running Eye Scan Measurements

Eye Scan tab lets you set up and run Eye Scan measurements

To select channels for the eye scan

To set the eye scan range and resolution

Scan Settings Subtab on

120

121

To quickly set up another measurement using the scale see

To run an eye scan measurement

To set advanced eye scan options

To set up qualified eye scan measurements

Advanced Subtab on

122

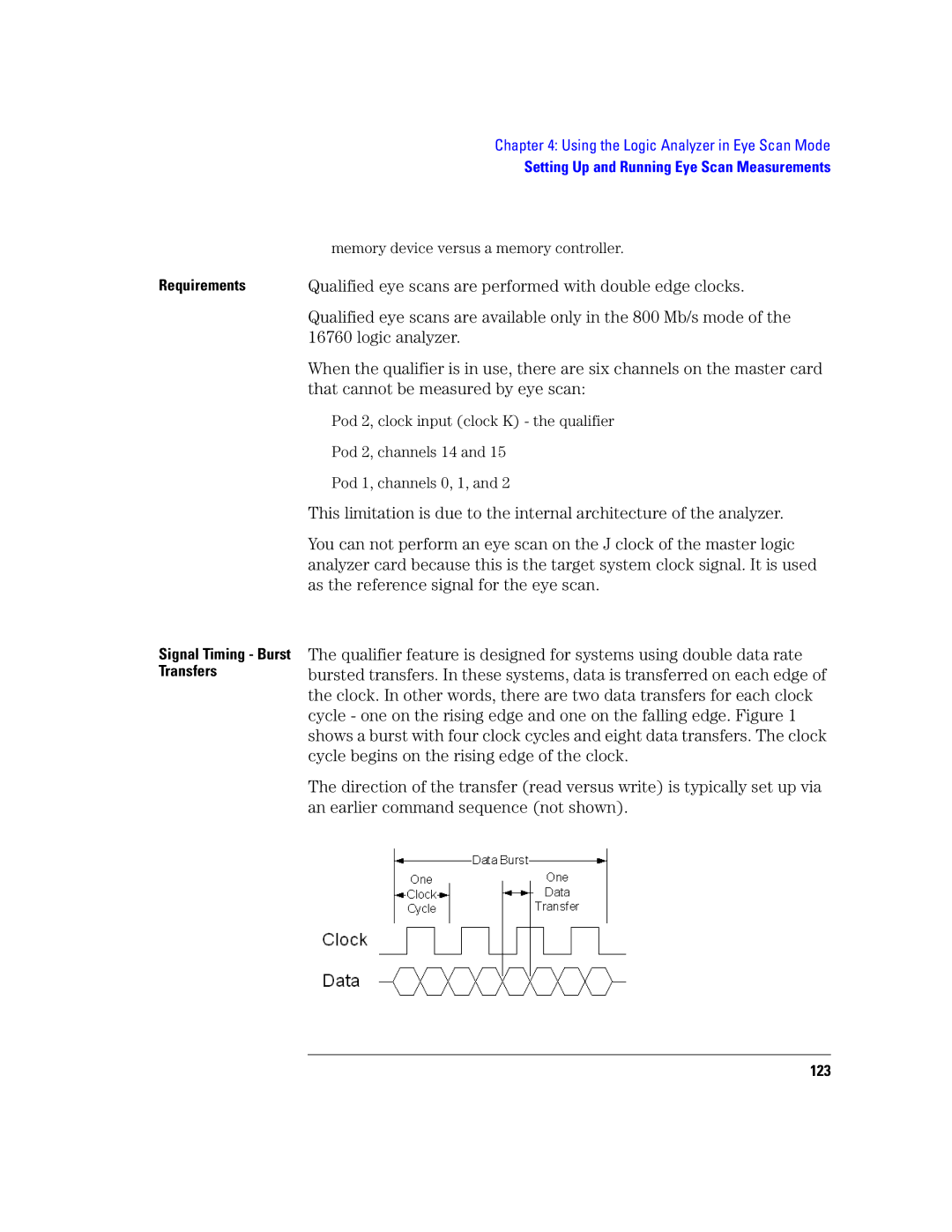

Requirements Signal Timing Burst Transfers

Memory device versus a memory controller

123

Before the clock edge to after it

Has adjustable sampling positions on each input channel

Burst

After the rising edge of the clock

Clock cycle of the next burst

Are supported

125

126

127

Be sure that the thresholds are set correctly

Display

For correct state mode acquisitions

Not already expanded

Start your target system and select Run Eye Finder

129

Now, set up eye scan mode

130

Select the Eye Scan tab Select the Qualifier subtab

131

Select the Qualify eye scan sampling using... button

To comment on the eye scan settings

Displaying Captured Eye Scan Data

To open the Eye Scan display

133

134

To select the channels displayed

Tool

Within the data captured on the bus

Eye Scan display window, select the Scale tab

To scale the Eye Scan display

Scale tab, you can

To use the scaling options

To open the Eye Scan display on

To quickly set up another measurement using the scale

To set Eye Scan display options

To clear the captured eye scan data

137

138

139

140

To change the Eye Scan color scale

Is zero by default

Make measurements on the eye scan data on

141

To make measurements on the eye scan data

About the captured measurement data

142

143

144

145

146

147

148

149

To display information about the eye scan data

Scroll bars to navigate through the information

Eye Scan display window, select the Info tab

150

Info tab, you can

151

To comment on the eye scan data

Loading Logic Analyzer Configurations on

Saving and Loading Captured Eye Scan Data

152

153

Sampling Tab on Format Tab on Trigger Tab on

154

Sampling Tab

Sampling tab lets you choose between the logic analyzers

155

156

Timing Mode

Conventional Transitional

Acquisition

Samples with transitions

How Samples are Stored in Transitional Timing

Will be stored

Period and other times more than two sample periods apart

State Mode

State Speed

158

159

Sampling Positions Dialog

Sampling Positions Tab

File menu Lets you save/load eye finder data

160

161

Label buttons

Display Area

Sampling Position

Cannot run the Eye Finder at this time

How the Selected Position Behaves

How the Suggested Position Behaves

XX% complete

163

Cannot run the Logic Analyzer at this time

Characterizer cannot be loaded

Complete Date

Select one or more labels in the Eye Finder Setup tab

165

Timeout N K clocks in 5 sec

This channel appears to be completely quiet

Two common possibilities exist

166

Run Eye Finder to characterize this channel

See individual channels for messages

Stable region extends beyond the limits of the display

Disk is probably full

Numerical value for the item XXX could not be read

Unsupported revision level AA.BB

Failed to open file for reading/writing Name

File Name already exists. Overwrite?

Invalid true/false flag

169

Eye Finder Setup Tab

170

Eye Finder Advanced Settings Dialog

171

File Info Tab

Save As

Eye Scan Mode

Reload

Save

173

Selecting the Eye Scan Mode on

Specify the logic analyzer pod and clock threshold voltages

Expander cards which cannot be used in the clock setup

Format Tab

Data

Pods

Pod Assignment Dialog

Name

Type

176

Trigger Tab

177

Trigger Functions Subtab

178

General Timing Trigger Functions

179

180

General State Trigger Functions

181

Find pattern1 eventually followed by pattern2

182

183

Advanced Trigger Functions

184

Searched for

Turbo State Trigger Functions

State Trigger Functions

Advanced pattern1 or pattern2

186

187

Half Channel State Trigger Functions

188

Settings Subtab

Count

Intermodule Control

Overview Subtab

This tab gives a picture of the trigger sequence

189

Group events

Default Storing Subtab

Event Specification List

At start Acquisition

Status Subtab

Save/Recall Subtab

191

192

Creating trigger function libraries

Multiple files

Symbols Tab

Two kinds of symbols are available

That you use to set up resource terms

194

Object file versions See Also

Symbols Selector Dialog

Matching Symbols

195

Search Pattern

Offset By Option

Address masking is done by the Align to x Byte option

Qualifies any address from 100C through 100F

Symbol File Formats

Align to x Byte Option

Byte option allows you to mask off an address

General-Purpose Ascii GPA Symbol File Format

107 file

198

GPA Record Format Summary

Format

199

Records

Definitions in the file

200

Last address of the section, in hexadecimal

Symbol representing the name of the section

Symbol representing the function name

First address of the section, in hexadecimal

202

You can specify symbols for variables using

Name of a file

Number of a line in the file, in decimal

203

Comments

Collapse Shows labels only Select All Selects all channels

Eye Scan Tab

Labels Subtab

Expand

Time

Scan Settings Subtab

Run Mode

Scan Range

206

Advanced Subtab

Custom

Short

Medium

Long

Names for

Qualifier Subtab

Qualification

Clock Edge to Sample

209

Comments Subtab

Calibration Messages

Calibration Tab

Calibration Instructions

Calibration Status

211

Error Messages

Branch expression is too complex

General Guidelines

212

213

Specific Guidelines 200 Mb/s State and all Timing Modes

214

If the following sequence does not compile

This one may

Specific Guidelines 400 Mb/s State Modes

215

Specific Guidelines 800 Mb/s State Mode

Specific Guidelines 1250/1500 Mb/s State Mode

216

217

Last sequence level calls goto next

Goto action specifies an undefined level

Hardware Initialization Failed

Possible Causes

Timing sampling mode, flags are are always available

Maximum of 32 Channels Per Label

Must assign another pod pair to specify actions for flags

No more Edge/Glitch resources available for this pod pair

220

Possible Solutions

No more Pattern resources available for this pod pair

Phrase some of the edges as patterns

No Trigger action found in the trace specification

Slow or Missing Clock

221

222

Trigger function initialization failure

223

Trigger inhibited during timing prestore

Trigger Specification is too complex

Then the approximate time is 32 seconds

Combiner resource allocation guidelines

Event

224

Waiting for Trigger

Misaligned boundaries for addresses

225

226

To save a trigger setup on

227

Specifications and Characteristics

Operating temperature 0 to 45 degrees C

Probes

E5378A Input Equivalent Circuit

E5378A Single-Ended Probe Specifications Characteristics

E5379A Differential Probe Specifications Characteristics

All specifications are marked by * asterisk

229

E5379A Input Equivalent Circuit

1500 Mb/s Sampling Mode Specifications and Characteristics

E5380A Input Equivalent Circuit

230

231

Characteristics

232

233

400 Mb/s Sampling Mode Specifications Characteristics

234

200 Mb/s Sampling Mode Specifications Characteristics

235

Conventional Timing Mode Specifications and Characteristics

Transitional Timing Mode Specifications and Characteristics

All specifications are marked by * asterisk

236

What is a Specification?

237

What is a Characteristic?

What is a Function Test?

Referred to as an operational accuracy calibration

238

239

Concepts

Understanding Logic Analyzer Triggering

Conveyor Belt Analogy

240

241

Conveyor belt analogy

Next Sequence Levels on

Summary of Triggering Capabilities

Sequence Levels

Next Summary of Triggering Capabilities on

243

Addr Data

244

Boolean Expressions

Next Ranges on

Branches

Edges

Ranges

Trigger Sequence for Module

Flags

Occurrence Counters and Global Counters

Next Flags on

An edge followed by an edge with a time limit

Timers

Next Timers on

An example trigger sequence to set up this measurement is

Needed

Default Storage

Storage Qualification

Next Storage Qualification on

250

Sequence Level Storage

251

Strategies for Setting Up Triggers

Next Strategies for Setting Up Triggers on

Trigger Functions

Agilent 16715A trigger user interface

Pattern2 occurring immediately after Pattern1

252

Same trigger as If/Then statements

Store range until pattern occurs

253

Next Document Your Trigger Sequences on

Setting Up Complex Triggers

Next Setting Up Complex Triggers on

Document Your Trigger Sequences

Inline documentation on an Agilent logic analyzer

Conclusions

Different parts of the trigger to describe how they work

Next Conclusions on

Understanding State Mode Sampling Positions

To accurately capture data on a bus

256

257

258

Window

259

Understanding Eye Scan Measurements

260

261

Measurements run simultaneously in parallel

Voltage resolution that can be set is 1 mV

Using the Logic Analyzer in Eye Scan Mode on

Are multiple logic analyzer cards in a module in this case

Glossary

Asterisk * See edge terms, glitch, and labels

263

264

Divided into 1K 64-state records

265

Debug mode See monitor

266

Ethernet address See link-level

267

268

269

Module/probe interconnect cable

By the channel width of the instrument

Processor probe See emulation

270

271

Measurements

272

273

274

275

Index

251

276

247

277

122

278

180

279

280

Label values, symbolic, 105 labels, 22

Positive logic

281

242

282

107

283

Wait for other machine to trigger

284

Publication Number 5988-9044EN January 1