User’s Manual

Series B Mainframes E1300B and E1301B

Page

Limitation Of Warranty

Warranty

Certification

Exclusive Remedies

Trademark Information

Safety Symbols

Printing History

According to ISO/IEC Guide 22 and EN

Declaration of Conformity

Suggested Sequence for Using the Manuals

Installation and Getting Started Guide

Agilent 75000 Series B Documentation

Manual Descriptions

Related Documents

About this Manual

Manual Content

Table of Contents

Downloading Device Drivers

Using the Mainframe

Controlling Instruments Using Gpib

System Instrument Command Reference

Error Messages

Specifications

Sending Binary Data Over RS-232

Connecting and Configuring a Display Terminal

Table of Contents

Getting Started

Using This Chapter

Mainframe Description

Optional Mainframe Memory

Mainframe Features Getting Started

Instrument Concept Getting Started

Instrument Definition

Instrument Logical Addresses Instrument Secondary Addresses

Introductory Programming Examples

Systdate 1990,1,13

Systtime 14,00,00

Getting Started

Front Panel Features

Using the Front Panel

Second Menu Tutorial

Using Menus

How to Set or Read the System Gpib Address

Using the System Instrument Menu

How to Display Logical Addresses or Instrument Information

How to Reset the System

Using the Other Instrument Menus

How to Open/Close Channels How to Scan Channels

Using the Front Panel

Reading Error Messages

Monitor Mode

Monitor Mode Display Annunciators

Trigsour Immscan @100105INIT

Executing Commands

Sourpulscoun Sourpulsper Initimm Trigsour IMM

Display Control Editing Keys

Key Descriptions

Menu Keys

Other Keys

Instrument Control Keys

Case of Difficulty

Problem Problem Cause/Solution

Instrument Menus

System Instrument Menu

Using the Display Terminal Interface

Control DTR Read

Test

Switchbox Menu

Using the Front Panel

Temp Tcouple

Scanning Voltmeter Menu

Unstrn

Agilent E1326B/E1411B 5 1/2 Digit Multimeter Standalone Menu

Agilent E1328A 4-Channel D/A Converter Menu

Agilent E1330A Quad 8-Bit Digital Input/Output Menu

Using the Front Panel

Agilent E1332A 4-Channel Counter/Totalizer Menu

Timeint CHAN1 Trigsour IMMMEAS1TINT?

Agilent E1333A 3-Channel Universal Counter Menu

CHAN2 Trigsour IMMMEAS2TINT?

Using the Front Panel

Using the Display Terminal Interface

Terminal Interface Features

Using Menus

How to Access the Utility Keys

Instrument Menu

Press f1 to Reset

How to Display Logical Addresses and Instrument Information

Is not being displayed press Utils then Selinst

How to Open/Close Channels

How to Display Module Type , Description, or Reset Module

Dispmonstat on

UTILS, RCLPREV, then Return

SYSTERR?

Sourpulscoun Sourpulsper Trigsour IMM Initimm

Executing Commands

Menu and Menu Control Keys

General Key Descriptions

Ctrl D = Select an instrument menu

Supported Terminals

Using Supported Terminals

Fields Value

Using the Display Terminal Interface

Using the WYSE WY-30

Using Other Terminals

What Not Supported Means Testing Terminals for Compatibility

Menu Name Instrument

Using a Terminal Without Menus

Instrument Names for the SI Command

Control Sequence Functions

Instrument Prompt then press D

Interface control

Using the Display Terminal Interface

Instrument Menus

System Instrument Menu

Control DTR Read

Switchbox Menu

Using the Display Terminal Interface

Scanning Voltmeter Menu

Unstrn

Agilent E1326B/E1411B 5 1/2 Digit Multimeter Standalone Menu

Agilent E1328A 4-Channel D/A Converter Menu

Agilent E1330A Quad 8-Bit Digital Input/Output Menu

Using the Display Terminal Interface

Agilent E1332A 4-Channel Counter/Totalizer Menu

Timeint CHAN1 Trigsour IMMMEAS1TINT?

Agilent E1333A 3-Channel Universal Counter Menu

CHAN2 Trigsour IMMMEAS2TINT?

Using the Display Terminal Interface

Using the Pacer

Using the Mainframe

Sourpulscoun INF

Abort

Sourpulsper 250E-3

Trigsour EXT

Systcommgpibaddr

Changing Primary Gpib Address

Synchronizing Internal External Instruments

Output 70914TRIGSOUR EXT

Output 722TRIG Extdcvmem Fifo

Output 70914OUTP on

Output 722TRIG Extdcv

Output 70914TRIGSOUR BUS

Output 70914INIT

Mainframe Data Memory

Using Mainframe Data Memory

Allocating a User Memory Segment

Non-Volatile User Memory

Ibasic Users

Locating the Nram

Real Addr,Size

Output 70900DIAGBOOT

Output 70900DIAGNRAMCRE

Wait

Using DOWNload UPload? to Access Data

Output 70900 Using Diagdown ,8D,,# 232,32B Addr+ 64,Bytes

Output 70900 Using Diagdown ,8D,,# 232,16W Addr+ 96,Words

Output 70900 Using Diagdown ,8D,,# 264,64A Addr,Chars$

Chars$= 1234567890123456789012345678901234567890

Downloading Device Drivers

Downloading Device Drivers

About this Chapter

Driver and Documentation Usage Downloading Device Drivers

Positioning of Allocatable RAM

Memory Configuration

Editing the Configuration File

Download Program Configuration

Downloading Device Drivers

Downloading Drivers in MS-DOS Systems

Progexec ’MSI ,700,1’

Downloading Drivers in Gpib Systems with

Downloading Drivers in Gpib Systems with Basic

Downloading Multiple Drivers

Checking Driver Status

Manually Downloading a Driverdown manual

Reboot the system

Preparing Memory for Manual Downloading

Defined the Driver RAM

Transmission Format

SYSTCOMMSERPACETHRSTOP? MAX

Diagcomm Stor

Systcommserpacethrstar

Systcommserpacexon

Asserted. This acts to pace the System Instrument output

Cat filename device file

Page

Downloading Device Drivers

Programming Hints

Controlling Instruments Using Gpib

Controlling Instruments Using Gpib

Status System Structure

Status Byte Register

Status Byte Register

Bit Decimal Number

Reading the Status Byte Register

Status Byte Register

SRE?

Print P

Unmasking Standard Event Status Bits

Standard Event Status Register

Standard Event Status Register

ESE

ESR?

ESE?

STATusOPERationENABle event

DIAGnosticINTerruptRESPonse?

STATusOPERationENABle?

Operation Status Group Condition Register

Output 70900 DIAGINTSETUP5 on Output 70900 Diagintact on

Enable Intr

CLS

Output 70900 Statoperenab

SUB Intrresp = SPOLL70900

Clearing Status

Interrupting an External Computer

Example Interrupting when an Error Occurs

Output 70909SOURVOLT1 5*OPC?

Synchronizing an External Computer Instruments

Enter 70909A

Enter 70903A

END While

Controlling Instruments Using Gpib

Command Types

System Instrument Command Reference

Common Command Format

System Instrument Command Reference

DIAGINTSETUP2?, DIAGINTPRI2 5, SYSTCOMMSER1BAUD

DIAGINTSETupn? and SYSTCOMMSERialnBAUD?

ROUTeSCANMODE?

SOURce PULSe COUNt COUNt? PERiod PERiod?

Indefinite Length Block

# non-zero digit digits data bytes

# 0 data bytes NL END

Rstoutp on Trigsour HOLD*TRG

Reference

Scpi Command

ABORt

Abort

Subsystem Syntax DIAGnostic

DIAGnostic

DIAGnostic

Related Commands Diagbootwarm

DIAGnosticBOOTCOLD

Re-booting the System Instrument cold

Diagbootcold

Diagbootwarm

DIAGnostic Bootwarm

Diagcommser Ibas Diagbootwarm

COMMunicate SERial0OWNer

SERial0OWNer?

COMMunicate

SERialnSTORe

DIAGCOMMSER?

DIAGnosticCHECkedDOWNloadMADDress address , data writes

Parameters DIAGnostic DOWNloadCHECked MADDress

Parameter Range Default Name Type

DOWNloadCHECked MADDress

Data Value Check Bits

DIAGnosticDOWNloadCHECked MADDress

1FC0016 + Laddr * 64 + registernumber

Parameters DIAGnostic DOWNloadCHECked SADDress

DOWNloadCHECked SADDress

DIAGnosticDOWNloadCHECked SADDress

DOWNload MADDress

Parameters DIAGnostic DOWNload MADDress

1FC00016 + Laddr * 64 + registernumber

DIAGnosticDOWNloadSADDress

Example Downloading Data to a Single Address Location

DIAGnostic DRAMAVAilable?

Diagdownsadd # H1FCA20,#

DIAGDRAMAVA?

DIAGnosticDRAMCREate size numdrivers creates a non-volatile

DIAGnosticDRAMCREate

DRAMCREate

Example Allocate a 15 Kbyte non-volatile Driver Ram segment

DRIVerLOAD

Parameters DIAGnostic DRIVerLOAD driverblock

Parameters Comments Example

Diagdrivload

DIAGDRIVLISTROM?

DIAGnosticDRIVer LISTtype?

Diagdrivlist ?

Read with the DIAGnosticINTerruptRESPonse? command

DIAGnostic INTerruptACTivate

Example Enable an Interrupt Acknowledgement on Line

INTerruptACTivate

Example Setup and wait for VXI interrupt response on line

DIAGnosticINTerruptSETupn?

DIAGINTSETUP2 on

Example Determine interrupt setup for line

INTerruptPRIorityn

DIAGnostic INTerruptPRIorityn

INTerruptPRIorityn?

DIAGINTPRI2

DIAGINTRESP?

DIAGnosticINTerruptRESPonse?

DIAGINTSETUP2 on

DIAGnosticNRAMCREate size

DIAGnostic NRAMADDRess?

NRAMCREate

DIAGNRAMADDR?

DIAGNRAMCREate?

DIAGnosticNRAMCREate?

DIAGPEEK? 16252928,8

Enter statement

DIAGnosticPOKE address , width , data writes data number

DIAGnostic Poke

Diagpoke 16252928,8,255

DIAGRDISADDR?

RDISkCREate

DIAGnosticRDISkCREate

Diagrdiscre

DIAGRDISCRE?

DIAGnosticUPLoadMADDress? address , bytecount Returns

DIAGnostic UPLoadMADDress?

Example Upload data stored on non-volatile User RAM

Output DIAGUPL? value of ADD ,1024

DIAGnosticUPLoadSADDress? address , bytecount Returns

DIAGnosticUPloadSADDress?

Example Upload data stored in non-volatile User RAM

Output DIAGUPLSADD? # H1FCA20,1024

INITiate

Related Commands ABORt, TRIGger

INITiate IMMediate

Init

PULSeCOUNt

SOURce

PULSeCOUNt?

Sourpulscoun 1E3

SOURPULSPER?

PULSePERiod

SOURce PULSePERiod

STATus

Example Reading the contents of the condition register

STATus OPERation CONDition?

STATOPERCOND?

Related Commands STATOPERENABle?

STATus OPERationENABle?

Example Presetting the Enable Register

STATus PRESet

Example Reading the Event Register

STATOPEREVEN?

SYSTem BEEPerIMMediate

SYSTem

Example Sound the Beeper

Systbeepimm

Example Set the Gpib port’s primary address

SYSTemCOMMunicate GPIBADDRess

Systcommgpibaddr

SYSTCOMMGPIBADDR?

SYSTCOMMSER0CONTDTR on

SYSTem COMMunicate SERialn CONTrol DTR Example

Parameters Comments

SYSTCOMMSER0CONTDTR?

Example Checking the setting of DTR control

SYSTemCOMMunicate SERialn CONTrol DTR?

SYSTCOMMSER0BAUD

Example SYSTem COMMunicate SERialn CONTrol RTS?

Example COMMunicate SERialn RECeive BAUD?

Example COMMunicate SERialn RECeive BITS?

SYSTemCOMMunicate SERialn RECeive Bits

SYSTCOMMSER0BITS

SYSTCOMMSER0BITS?

Pace PROTocol?

Pace PROTocol

SYSTem COMMunicate SERialn RECeive Pace PROTocol

SYSTCOMMSER0PACEPROT XON

SYSTemCOMMunicateSERial n RECeive PACETHResholdSTARt

SYSTemCOMMunicate SERialn RECeive Pace THReshold STARt

SYSTCOMMSER0PACETHRSTAR

Example Return current start threshold

SYSTCOMMSER0PACETHRSTOP

SYSTemCOMMunicateSERial n RECeive PACETHResholdSTOP

Example Return current stop threshold

SYSTCOMMSER0PACETHRSTOP?query for threshold

SERialn RECeive

PARity CHECk?

PARity Type

SYSTCOMMSER0PARCHEC on

SYSTCOMMSER0PAR ODD

SYSTem COMMunicate SERialn RECeive PARity Type

SBITs

PARity TYPE?

SYSTemCOMMunicate SERialn RECeive PARity TYPE?

SYSTCOMMSER0PAR?

SYSTCOMMSER0TRANAUTO on

SYSTemCOMMunicateSERialnRECeiveSBITs? MIN MAX returns

Example Is Auto on or OFF?

SYSTCOMMSER0TRANAUTO?

SYSTCOMMSER0TRANPACEPROT?

SYSTemCOMMunicate SERialnTRANsmit Pace PROTocol

SYSTCOMMSER0TRANPACEPROT XON

SYSTem DATE?

Example Setting the system Date

Systdate 1991,09,08

DATE? SYSTemDATE? MIN MAX,MIN MAX,MIN MAX returns

Systtime 14,30,20

SYSTemTIME

SYSTTIME?

Input values of hour,min,sec

TRIGger DELay

DELay

Trigdelay .75 S

TRIGger

Triggering the Pacer

TRIGgerIMMediate

Trig

Discrete NEGative None

RST Condition Trigsour IMM

TRIGger SOURce?

Parameter Value Source of Trigger

VXICONFigure DLADdress?

CONFigure DLADdress?

Example Determining the device addresses within the system

VXICONFDLAD?

N1, n2, n3, n4, n5, n6, c1, c2, c3, c4, c5, s1, s2, s3, s4

VXI CONFigureDLISt?

N1 Device’s Logical Address. a number from 0 to

N6 Slot 0 Logical Address. a number from 0 to

Example Querying the device list for the System Instrument

VXICONFigure DNUMber? Parameters

Example Determining the number of devices within the system

VXICONFDNUM?

VXI CONFigure HIERarchy?

CONFigure HIERarchy?

VXICONFigure HIERarchyALL?

CONFigure HIERarchyALL?

CONFigure INFormation?

VXICONFINF?

Example Query information on logical address

Vxisel

CONFigure LADDress?

CONFigure INFormationALL?

VXICONFigure INFormationALL?

Related Commands VXICONFNUMB?

Numericvalue or the following optional words

Example Read from one of a device’s configuration registers

VXI REGisterREAD?

VXIREGisterWRITe

Related Commands Vxisel

VXI SELect

SELect

Vxiwrit 8,24,# H4200

VXIWRITe

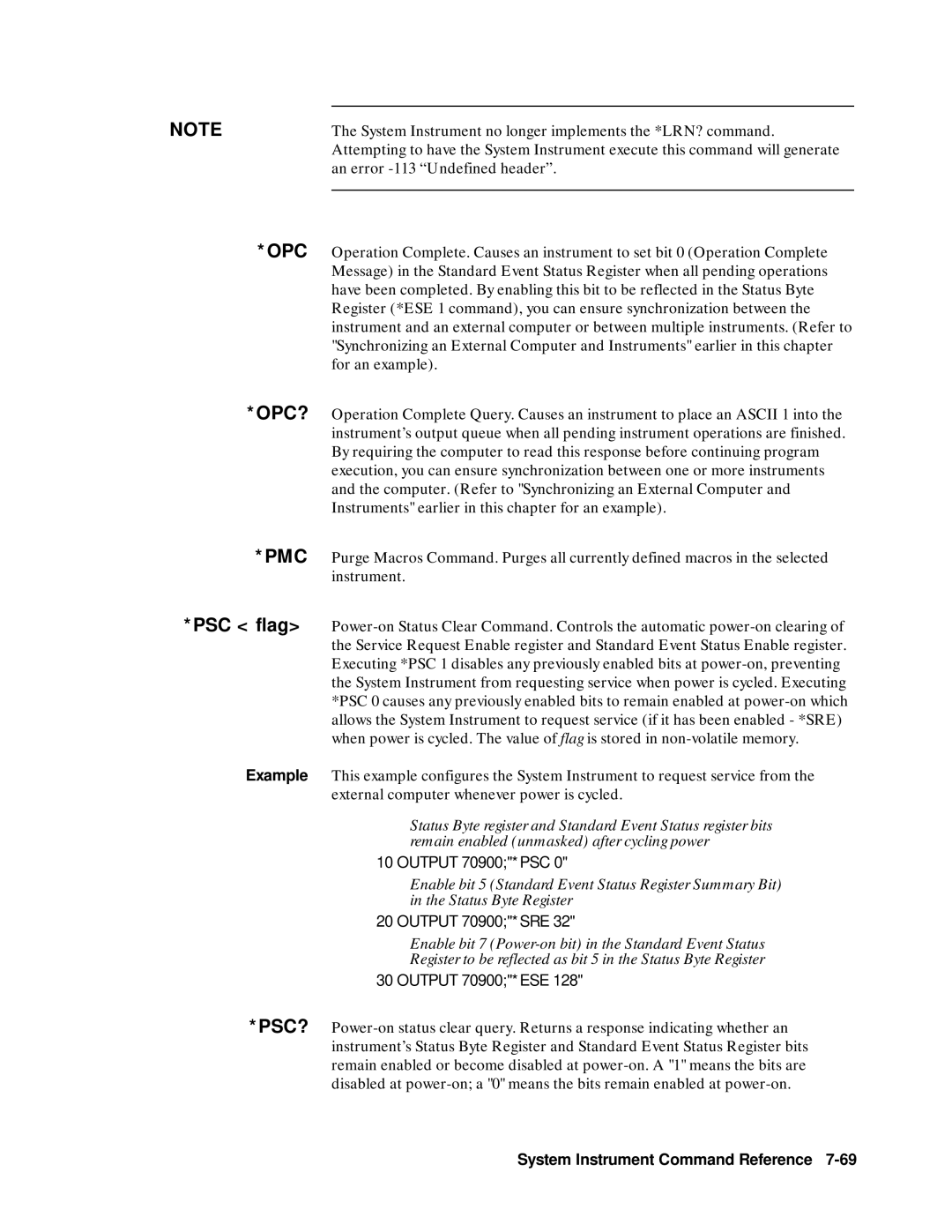

Common Command Reference

Output 70900*DMC ’LIST’,# 0VXICONFDLIS?

DMC namestring Commandblock

Output 70900*ESR?

Output 70900*ESE?

Enter 70900A

Print A$

Example Get the ID fields from the system and print them

Output 70900*ESE

Output 70900*PSC

Output 70900*SRE

Output 70900*SRE

Print a

Output 70900*SRE?

Go To Local GTL

Gpib Message

Group Execute Trigger GET

Interface Clear IFC

Local Lockout LLO

Device Clear DCL or Selected Device Clear SDC

Remote

Serial Poll Spoll

Remote

10 P= Spoll

Scpi Commands Quick Reference

Command Quick Reference

Command Description

Command Quick Reference

Nram

BAUD? MIN MAX

VXI

Synchronization

Instrument Status

Macros

Command Quick Reference

Mainframe Specifications

Specifications

Specifications A-1

Trigger Input Non-volatile added memory storage lifetime

Power

Weight

Operating temperature

Storage temperature

Table A-1. Switchbox SCPI-1990.0 Confirmed Commands

Switchbox Configuration

Table A-2. Switchbox Non-SCPI Commands

Specifications A-3

Table A-4. Multimeter Scpi Approved not confirmed Commands

Table A-3. Multimeter SCPI-1990.0 Confirmed Commands

Specifications A-5

Table A-5. Multimeter Non-SCPI Commands

Table A-7. Agilent E1332A Non-SCPI Commands

Table A-6. Agilent E1332A SCPI-1990.0 Confirmed Commands

Specifications A-7

Table A-8. Agilent E1333A SCPI-1990.0 Confirmed Commands

Table A-9. Agilent E1333A Non-SCPI Commands

Table A-11. Agilent E1328A Non-SCPI Commands

Commands

Table A-10. Agilent E1328A SCPI-1990.0 Confirmed Commands

Specifications A-9

Table A-12. Agilent E1330A SCPI-1990.0 Confirmed Commands

Table A-13. Agilent E1330A Non-SCPI Commands

Table A-16. System Instrument SCPI-1992.0 Approved Commands

Table A-15. System Instrument SCPI-1991.0 Confirmed Commands

Specifications A-11

Table A-17. System Instrument Non-SCPI Commands

Table A-18. Common Commands SCPI-1990.0 Confirmed

Specifications

Reading an Instrument’s Error Queue

Error Messages

Error number , error description string

Error Messages B-1

Error Number Error Type

Error Types

Table B-1. Negative Error Numbers

Error Messages B-3

Table B-2. Error Messages and Causes

Error Messages and Causes Code

2110

Table B-3. Start-up Error Messages and Warnings

Start-up Error Messages

Start-Up Error Messages and Warnings Code Cause

Error Messages B-5

Error Messages

Connecting a Terminal to the Mainframe

Connecting and Configuring a Display Terminal

Connecting and Configuring a Display Terminal C-1

Overview

To Connect to Gpib

Connecting and Configuring a Display Terminal C-3

Configuring a Terminal for the Mainframe

Configuring the Terminal

Configuring the Mainframe with Menus

Connecting and Configuring a Display Terminal C-5

How to Use the Serial Interface Menus

How to Store the Serial Interface Configuration

Formatting Binary Data for RS-232 Transmission

Sending Binary Data Over RS-232

Bit #

Sending Binary Data Over RS-232 D-1

Sending Binary Data Over RS-232

Setting Up the Mainframe

Table D-1. Correction Codes for RS-232 Transmission

Sending Binary Data Over RS-232

Sending Binary Data Over RS-232 D-3

Sending Binary Data Over RS-232

Index-1

Index

Systdate

Index-2

Index-3

Index-4

Index-5

Index-6

VXIREGREAD?

Index-7

Index-8