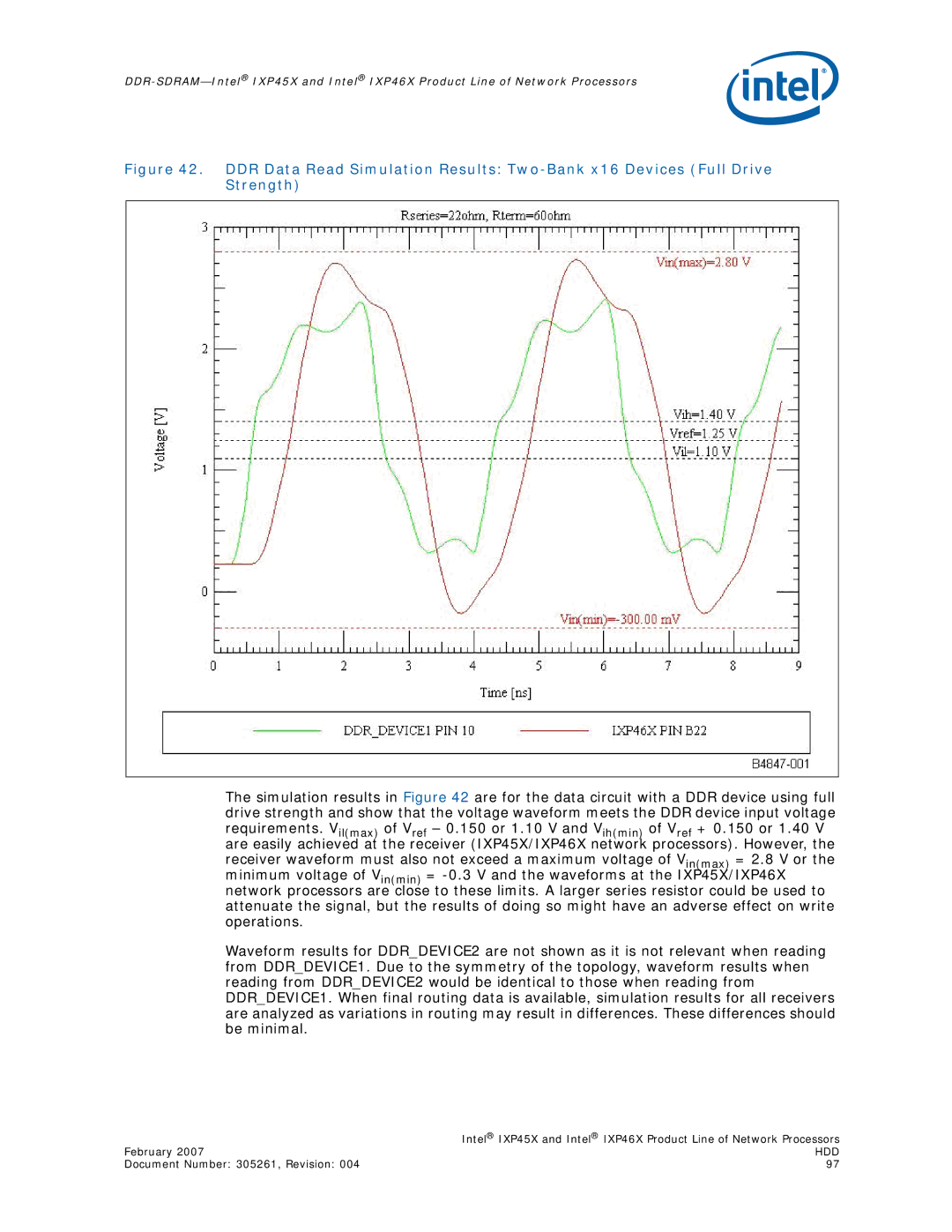

Figure 42. DDR Data Read Simulation Results: Two-Bank x16 Devices (Full Drive Strength)

The simulation results in Figure 42 are for the data circuit with a DDR device using full drive strength and show that the voltage waveform meets the DDR device input voltage requirements. Vil(max) of Vref – 0.150 or 1.10 V and Vih(min) of Vref + 0.150 or 1.40 V are easily achieved at the receiver (IXP45X/IXP46X network processors). However, the receiver waveform must also not exceed a maximum voltage of Vin(max) = 2.8 V or the minimum voltage of Vin(min) =

Waveform results for DDR_DEVICE2 are not shown as it is not relevant when reading from DDR_DEVICE1. Due to the symmetry of the topology, waveform results when reading from DDR_DEVICE2 would be identical to those when reading from DDR_DEVICE1. When final routing data is available, simulation results for all receivers are analyzed as variations in routing may result in differences. These differences should be minimal.

| Intel® IXP45X and Intel® IXP46X Product Line of Network Processors |

February 2007 | HDD |

Document Number: 305261, Revision: 004 | 97 |