Intel® IXP45X and Intel® IXP46X Product Line of Network

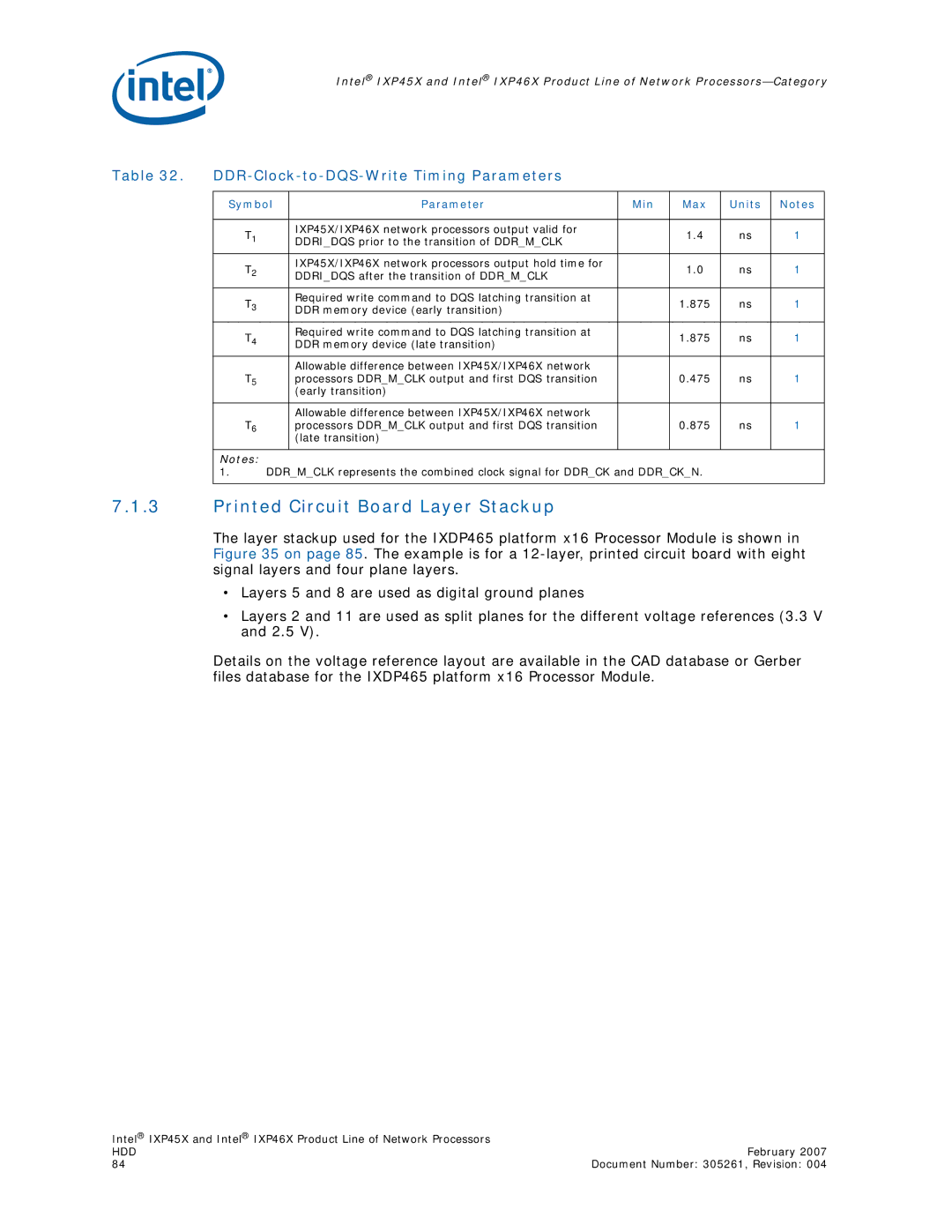

Table 32. |

|

|

|

|

| ||

|

|

|

|

|

|

| |

| Symbol | Parameter | Min | Max | Units | Notes | |

|

|

|

|

|

|

|

|

| T1 |

| IXP45X/IXP46X network processors output valid for |

| 1.4 | ns | 1 |

|

| DDRI_DQS prior to the transition of DDR_M_CLK |

| ||||

| T2 |

| IXP45X/IXP46X network processors output hold time for |

| 1.0 | ns | 1 |

|

| DDRI_DQS after the transition of DDR_M_CLK |

| ||||

|

|

|

|

|

|

|

|

| T3 |

| Required write command to DQS latching transition at |

| 1.875 | ns | 1 |

|

| DDR memory device (early transition) |

| ||||

|

|

|

|

|

|

|

|

| T4 |

| Required write command to DQS latching transition at |

| 1.875 | ns | 1 |

|

| DDR memory device (late transition) |

| ||||

|

|

|

|

|

|

|

|

|

|

| Allowable difference between IXP45X/IXP46X network |

|

|

|

|

| T5 |

| processors DDR_M_CLK output and first DQS transition |

| 0.475 | ns | 1 |

|

|

| (early transition) |

|

|

|

|

|

|

|

|

|

|

|

|

| T6 |

| Allowable difference between IXP45X/IXP46X network |

|

|

|

|

|

| processors DDR_M_CLK output and first DQS transition |

| 0.875 | ns | 1 | |

|

|

| (late transition) |

|

|

|

|

|

|

|

|

|

|

|

|

| Notes: |

|

|

|

|

|

|

| 1. | DDR_M_CLK represents the combined clock signal for DDR_CK and DDR_CK_N. |

|

| |||

|

|

|

|

|

|

|

|

7.1.3Printed Circuit Board Layer Stackup

The layer stackup used for the IXDP465 platform x16 Processor Module is shown in Figure 35 on page 85. The example is for a

•Layers 5 and 8 are used as digital ground planes

•Layers 2 and 11 are used as split planes for the different voltage references (3.3 V and 2.5 V).

Details on the voltage reference layout are available in the CAD database or Gerber files database for the IXDP465 platform x16 Processor Module.

Intel® IXP45X and Intel® IXP46X Product Line of Network Processors |

|

HDD | February 2007 |

84 | Document Number: 305261, Revision: 004 |